Design and implementation of digital delay and pulse generator of BEPC II linear accelerator

-

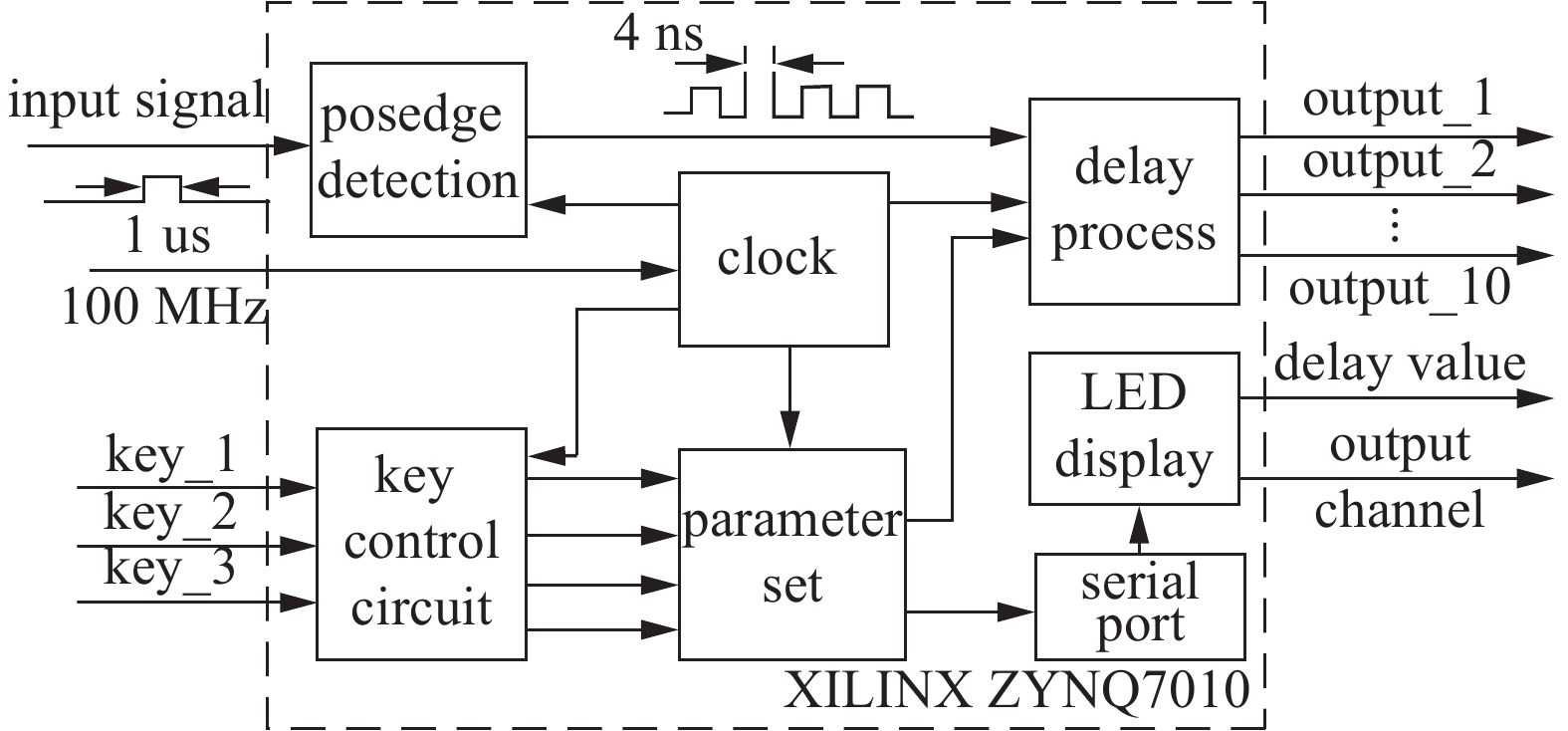

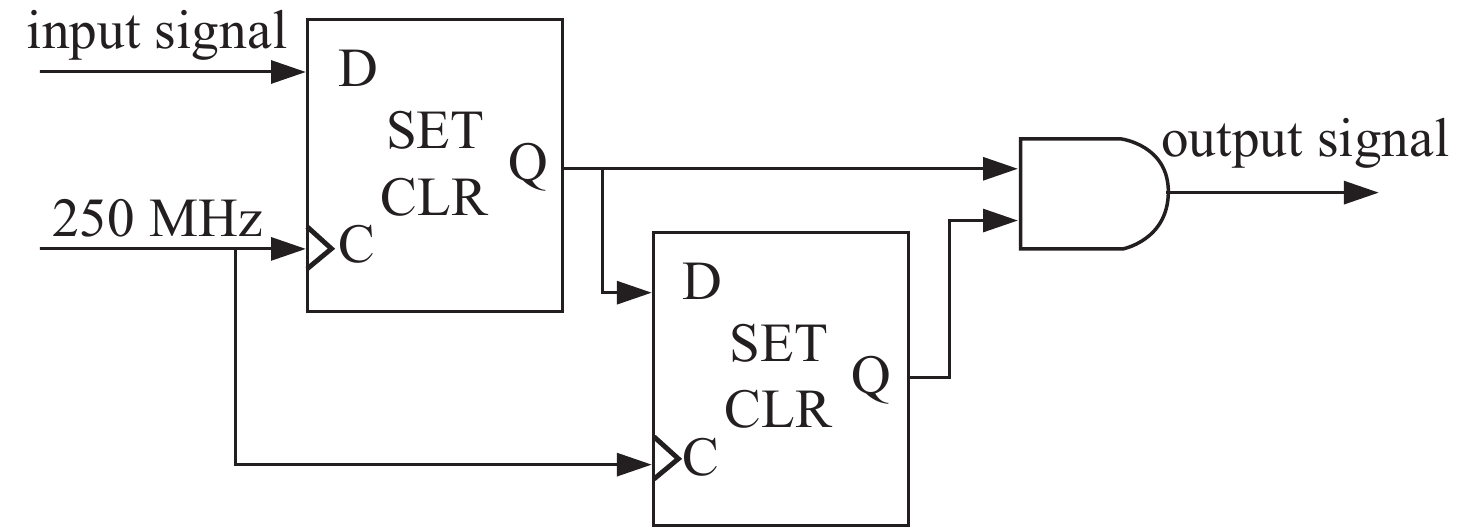

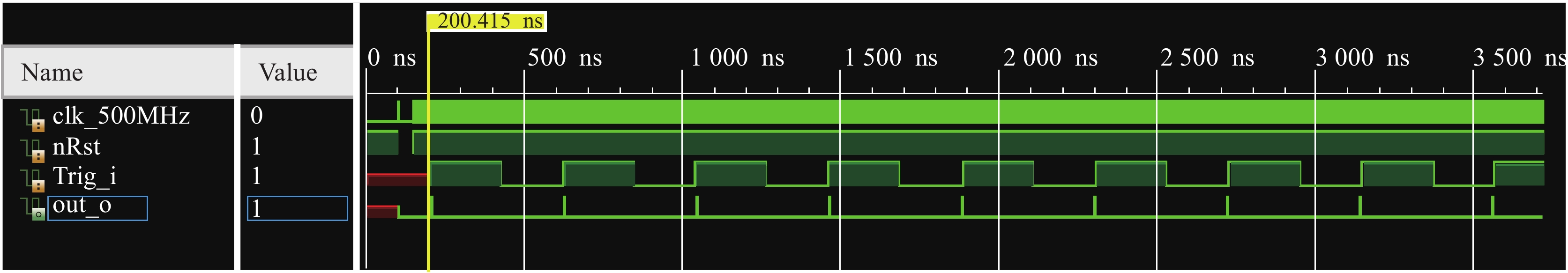

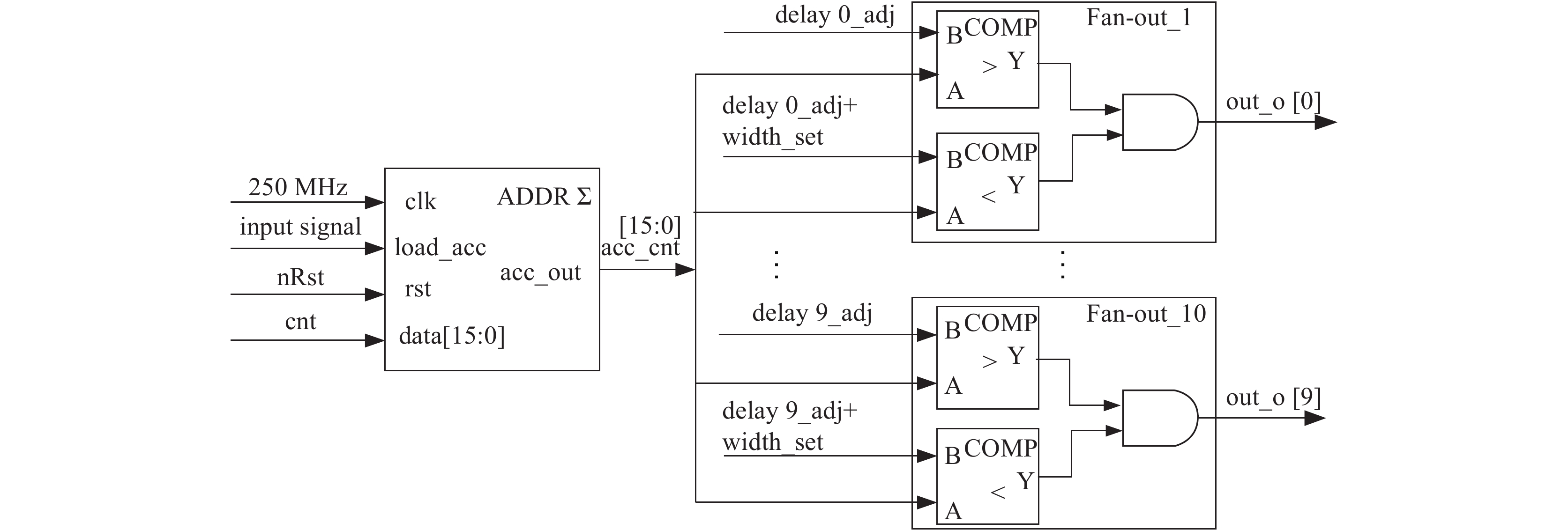

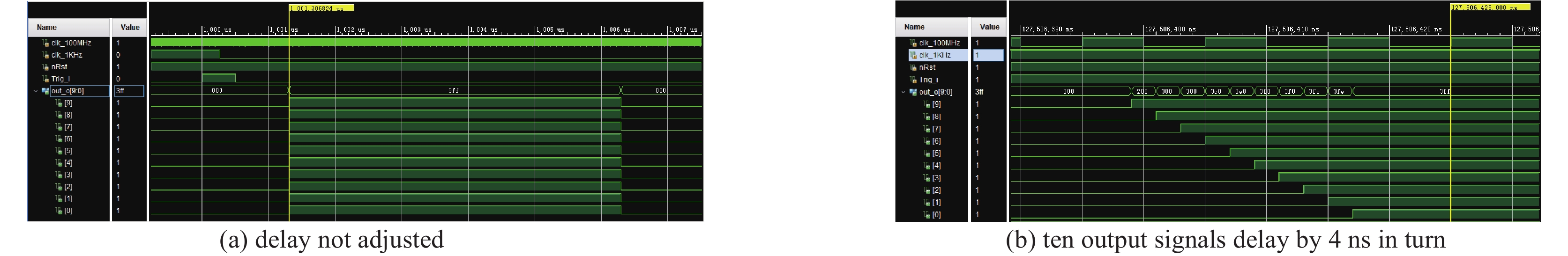

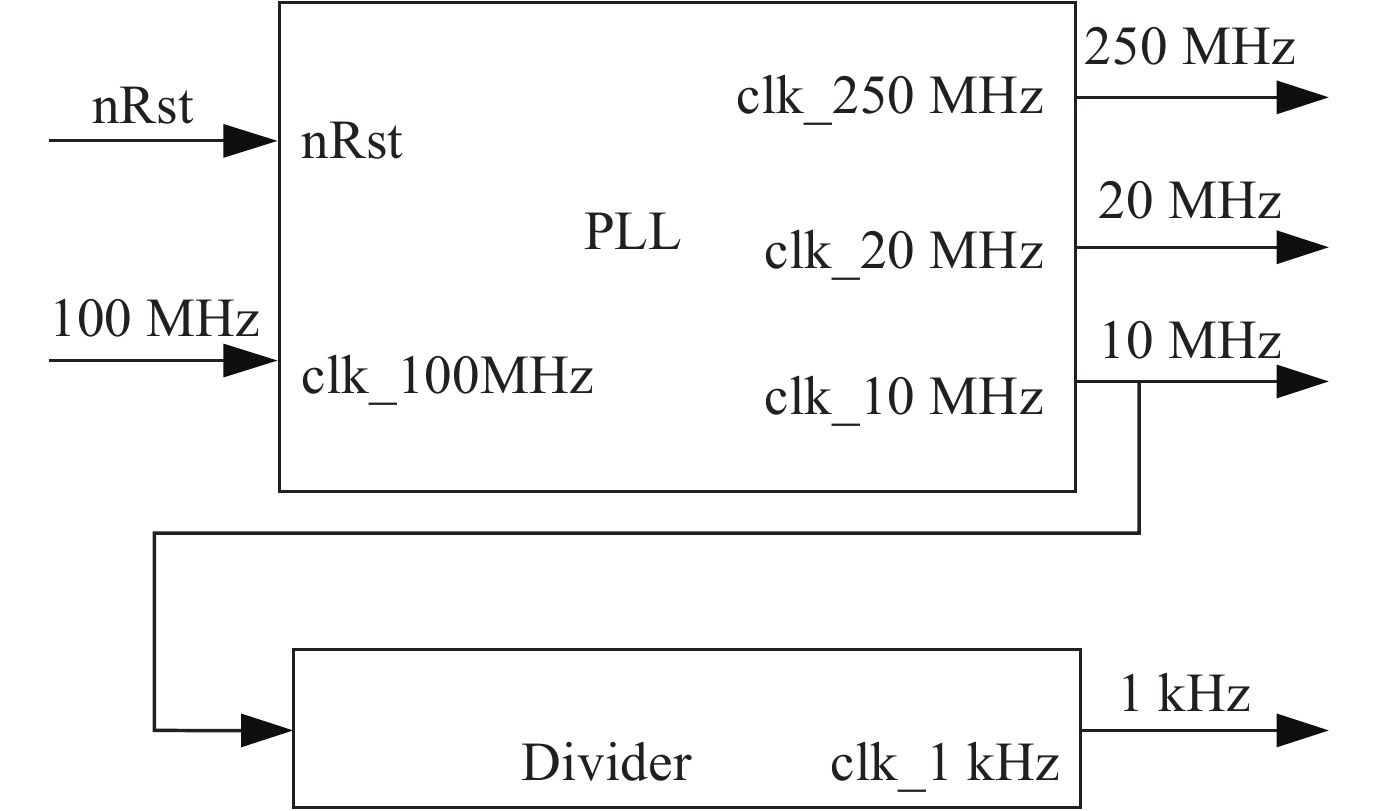

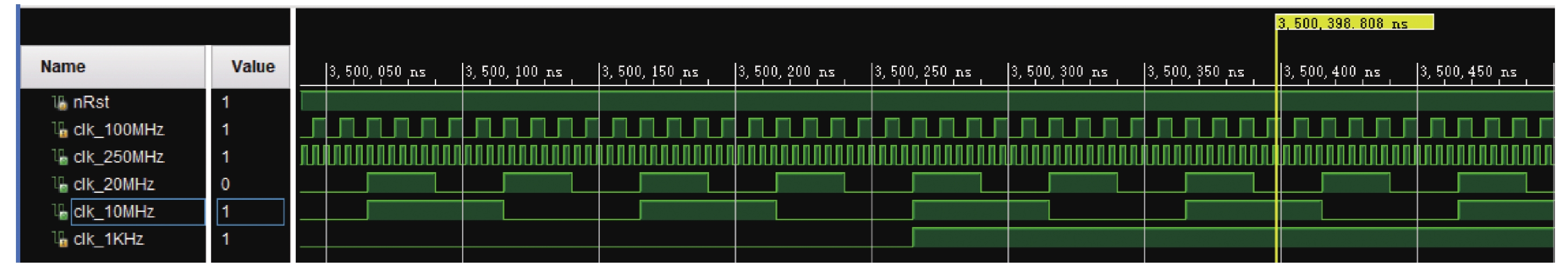

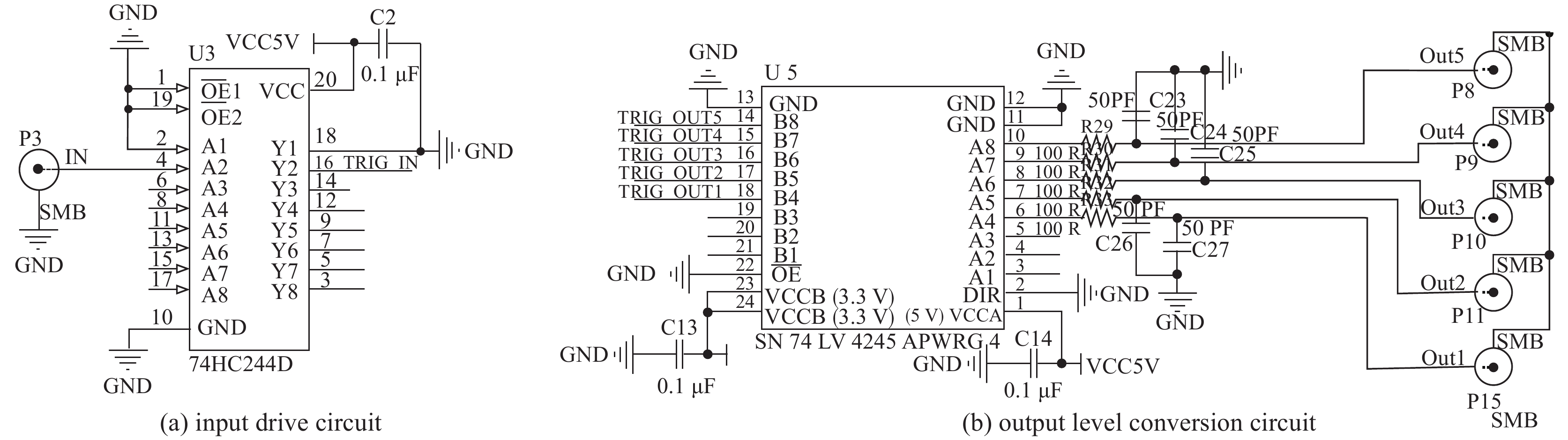

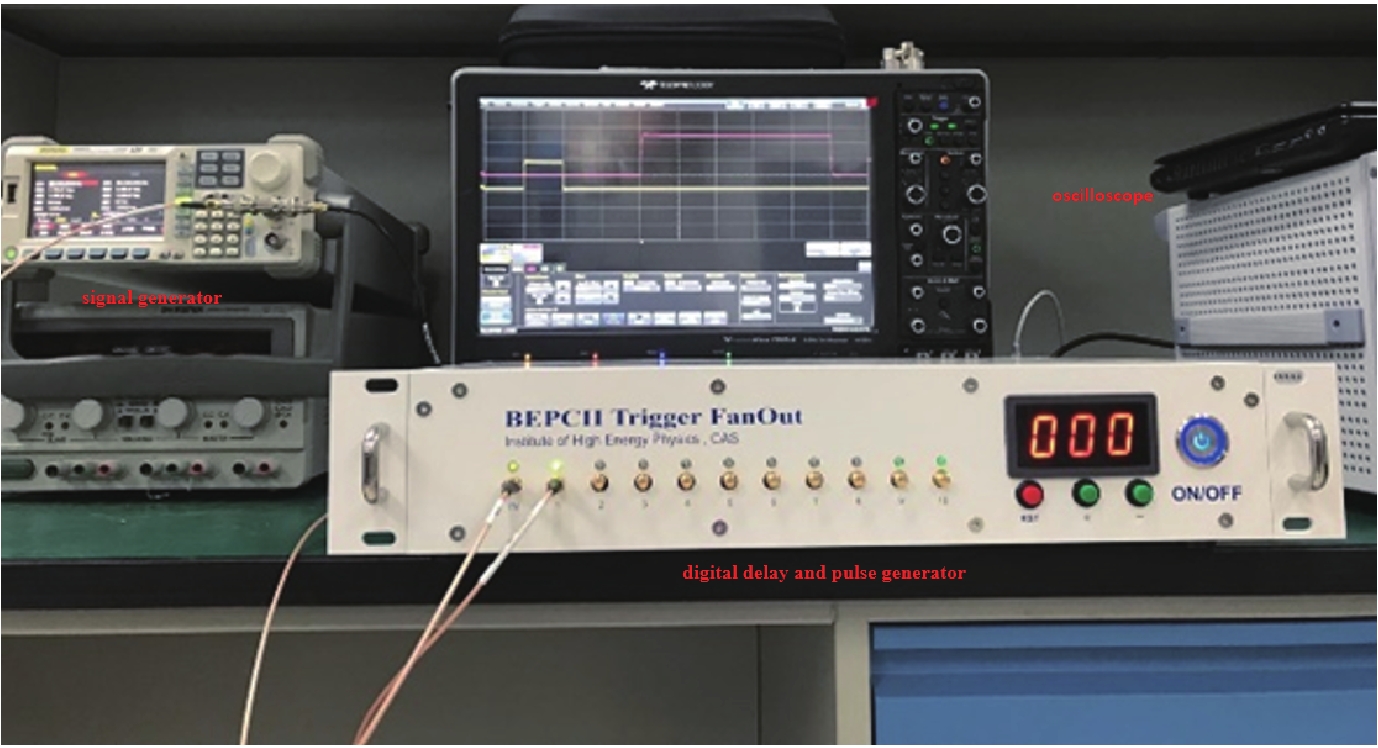

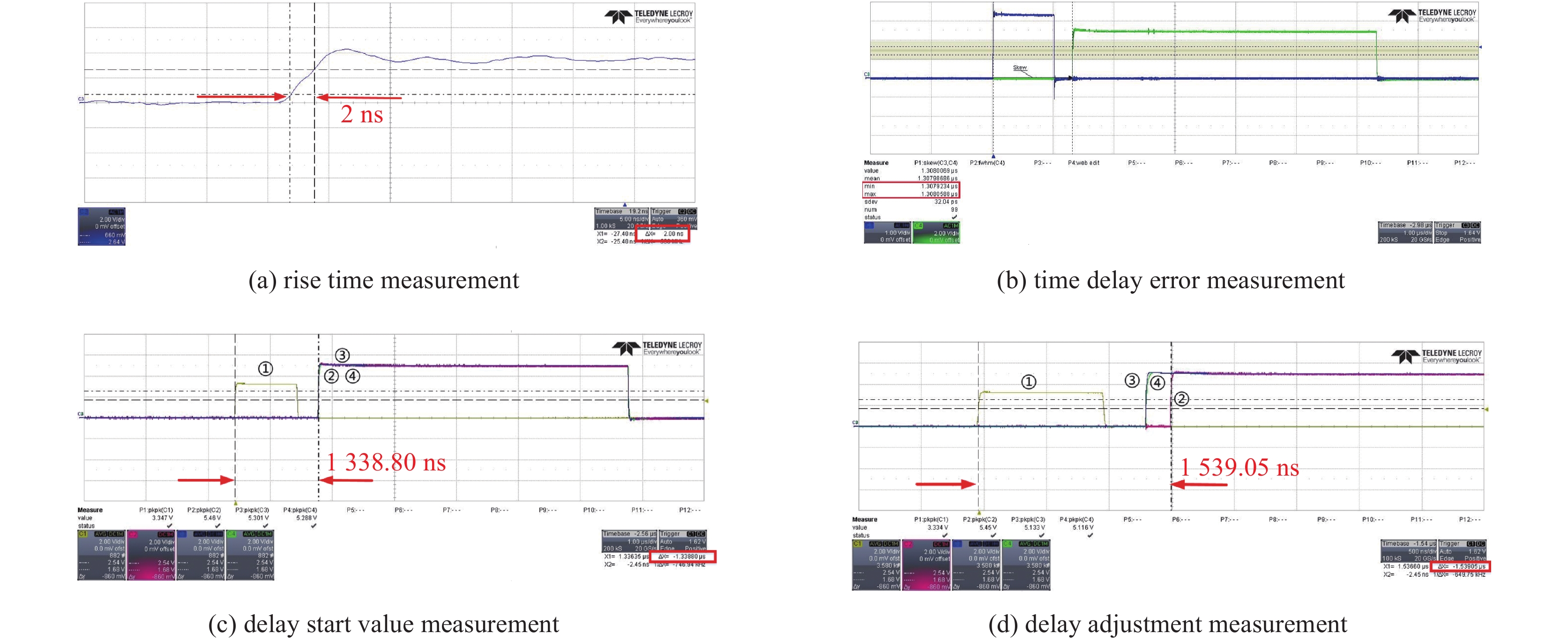

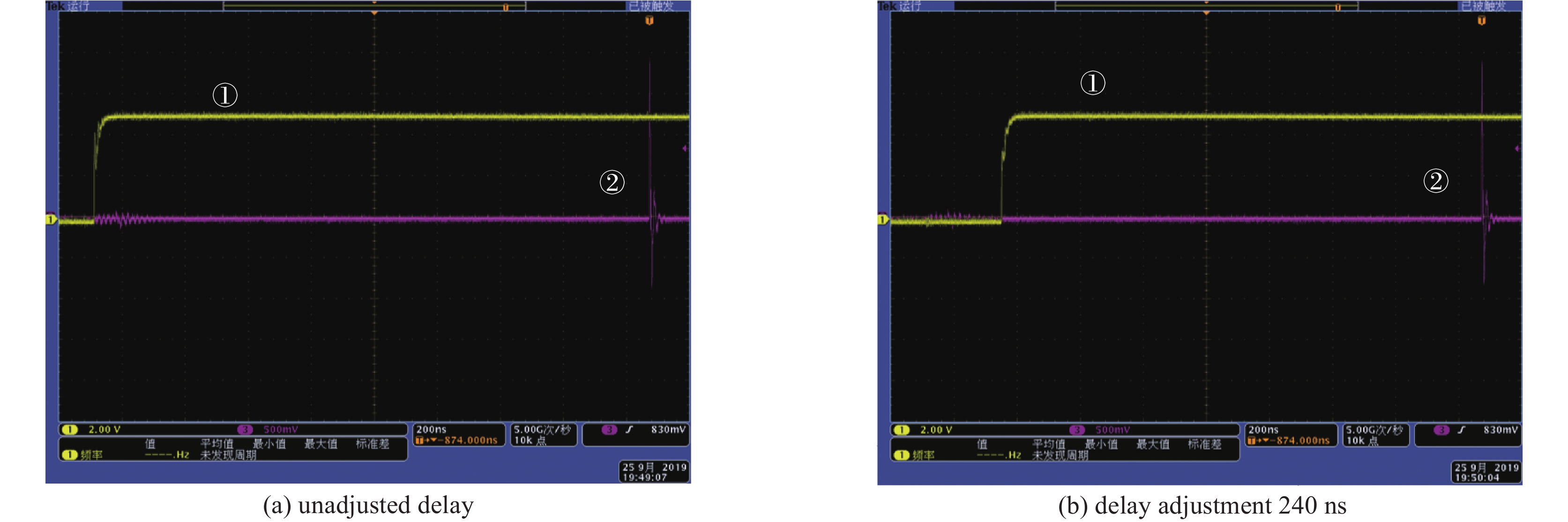

摘要: 针对北京正负电子对撞机II期(BEPC II)直线加速器升级改造过程中束流位置探测器(BPM)电子学对外部触发信号的需求,设计了一台高精度延时控制、上升时间短和参数灵活调节的数字延时触发器。采用FPGA(现场可编程门阵列)作为主控制器展开设计,重点介绍了基于FPGA的边沿检测模块和多通道延时处理模块的设计与仿真,描述了FPGA和驱动电路的设计方案以及在直线加速器上的应用。经测试,延时可调范围4 ns~4 μs,最小步进4 ns,步进误差0.125%;上升时间2 ns,延时抖动135.4 ps。Abstract: A digital delay and pulse generator with high precision delay control, short rise time and flexible parameter adjustment is designed to meet the needs of BPM electronics for external trigger signals in the process of upgrading the BEPC II linear accelerator. An FPGA is used as the main controller. This paper mainly introduces the design principle and simulation results of edge detection module and multi-channel delay processing module based on FPGA software platform, and describes the design of FPGA and drive circuit, and its application in linear accelerator. The test results show that the output pulse of the digital delay generator has an adjustable delay range of 4 ns~4 μs, a minimum step of 4 ns, an adjustable error of 0.125%, a rise time of 2 ns, and a delay jitter of 135.4 ps.

-

Key words:

- linear accelerator /

- FPGA /

- adjustable delay /

- rise time /

- multiple fan-out /

- driver circuit

-

表 1 数字延时触发器的参数需求

Table 1. Parameter requirements for digital delay and pulse generator

pulse width/μs fixed delay/μs range of adjustable delay/ns minimum step/ns rise time/ns output channels output voltage/V 5 1.3 4~1 000 4 <16 10 5 -

[1] 麻惠洲, 曹建社, 马力, 等. 利用数字束流位置处理器Libera测量BEPCII储存环束流阻尼时间和残余振荡[J]. 核电子学与探测技术, 2009, 29(3):525-528. (Ma Huizhou, Cao Jianshe, Ma Li, et al. BEPCII storage loop beam damping time and residual oscillations were measured using Libera digital beam position processor[J]. Nuclear Electronics and Detection Technology, 2009, 29(3): 525-528 doi: 10.3969/j.issn.0258-0934.2009.03.009 [2] 雷革, 徐广磊, 汪林, 等. BEPCII事件定时系统[J]. 核电子学与探测技术, 2008, 28(3):451-455, 469. (Lei Ge, Xu Guanglei, Wang Lin, et al. BEPCII event timing system[J]. Nuclear electronics and detection technology, 2008, 28(3): 451-455, 469 doi: 10.3969/j.issn.0258-0934.2008.03.001 [3] 赵岩, 翟百臣, 王建立, 等. 激光距离选通成像同步控制系统的设计与实现[J]. 红外与激光工程, 2008, 20(5):844-847. (Zhao Yan, Zhai Baichen, Wang Jianli, et al. Design and implementation of the laser range-gating imaging synchronization control system[J]. Infrared and Laser Engineering, 2008, 20(5): 844-847 [4] 李文峰, 邵涛, 张东东, 等. 重复频率纳秒脉冲源程控脉冲发生器[J]. 强激光与粒子束, 2012, 24(5):1186-1190. (Li Wenfeng, Shao Tao, Zhang Dongdong, et al. Repeat frequency nanosecond pulse source programmable pulse generator[J]. High Power Laser and Particle Beams, 2012, 24(5): 1186-1190 doi: 10.3788/HPLPB20122405.1186 [5] 潘泽跃, 程健, 陈园园. 基于FPGA的脉冲电源及其控制系统设计[J]. 强激光与粒子束, 2015, 27:095004. (Pan Zeyue, Cheng Jian, Chen Yuanyuan. Design of pulse power supply and control system based on FPGA[J]. High Power Laser and Particle Beams, 2015, 27: 095004 doi: 10.11884/HPLPB201527.095004 [6] 黄自江, 何衡湘, 姜忠明, 等. 高精度组合脉冲激光时序控制系统设计[J]. 强激光与粒子束, 2016, 28:125005. (Huang Zijiang, He Hengxiang, Jiang Zhongming, et al. Design of timing control system for high-precision combined pulsed laser[J]. High Power Laser and Particle Beams, 2016, 28: 125005 doi: 10.11884/HPLPB201628.160157 [7] 刘坤, 马进, 张东东, 等. 脉冲功率电源模块时序放电控制系统设计[J]. 强激光与粒子束, 2018, 30:035002. (Liu Kun, Ma Jin, Zhang Dongdong, et al. Design of sequential discharge control system for pulse power supply module[J]. High Power Laser and Particle Beams, 2018, 30: 035002 [8] 杨金宝, 曹忆南, 范松涛, 等. 百皮秒级三维选通成像时序控制系统[J]. 红外与激光工程, 2012, 41(7):1793-1794. (Yang Jinbao, Cao Yi’nan, Fan Songtao, et al. Hundred ps level timing control system in 3D range-gated imaging[J]. Infrared and Laser Engineering, 2012, 41(7): 1793-1794 [9] 徐卫彬, 郭玉辉, 郑亚伟, 等. 基于现场可编程门阵列的加速器同步控制器设计[J]. 强激光与粒子束, 2015, 27:015101. (Xu Weibin, Guo Yuhui, Zheng Yawei, et al. Design of synchronous controller for accelerator based on FPGA[J]. High Power Laser and Particle Beams, 2015, 27: 015101 doi: 10.3788/HPLPB20152701.15101 [10] 李玺钦, 马成刚, 赵娟, 等. 多通道可延时同步脉冲产生系统研究[J]. 电子设计工程, 2016, 24(8):44-46, 49. (Li Xiqin, Ma Chenggang, Zhao Juan, et al. Research on multi-channel delay synchronous pulse generation system[J]. Electronic Design Engineering, 2016, 24(8): 44-46, 49 [11] 王永鹏, 郭玉辉, 罗冰峰, 等. 基于FPGA技术的加速器切束控制系统设计[J]. 强激光与粒子束, 2016, 28:105103. (Wang Yongpeng, Guo Yuhui, Luo Bingfeng, et al. Design of beam cutting control system of accelerator based on FPGA[J]. High Power Laser and Particle Beams, 2016, 28: 105103 doi: 10.11884/HPLPB201628.160004 [12] 赵金栋. 基于FPGA的多路脉冲信号同步测量技术研究[D]. 哈尔滨: 哈尔滨工业大学, 2013.Zhao Jindong. Research on multi-channel pulse signal synchronization measurement technology based on FPGA [D]. Harbin: Harbin Institute of Technology, 2013 [13] 黄玉. 差分跳频通信系统的研究与FPGA实现[D]. 大连: 大连海事大学, 2014.Huang Yu. Research on differential frequency-hopping communication system and FPGA implementation[D]. Dalian: Dalian Maritime University, 2014 [14] 刘健, 陈弟虎, 粟涛. 一种FPGA芯片在射频干扰下的失效机理[J]. 强激光与粒子束, 2019, 31:093201. (Liu Jian, Chen Dihu, Su Tao. Failure mechanism of FPGA chip under RF interference[J]. High Power Laser and Particle Beams, 2019, 31: 093201 doi: 10.11884/HPLPB201931.190161 [15] 刘军. 极窄脉冲合成与超快沿产生电路设计[D]. 成都: 电子科技大学, 2019.Liu Jun. Very narrow pulse synthesis and ultra fast edge generation circuit design[D]. Chengdu: University of Electronic Science and Technology of China, 2019 [16] 龚文煊. BESⅢ触发系统时钟同步与束团产生电路的设计与实现[C]//第十三届全国核电子学与核探测技术学术年会论文集(上册). 2006: 48-54.Gong Wenxuan. Design and implementation of clock synchronization and bunch generation circuit in BES Ⅲ trigger system[C]//The Thirteenth Session of the National Nuclear Electronics and Nuclear Detection Technology Academic Essays (I). 2006: 48-54 -

下载:

下载: