High-precision multi-channel pulse delay technology

-

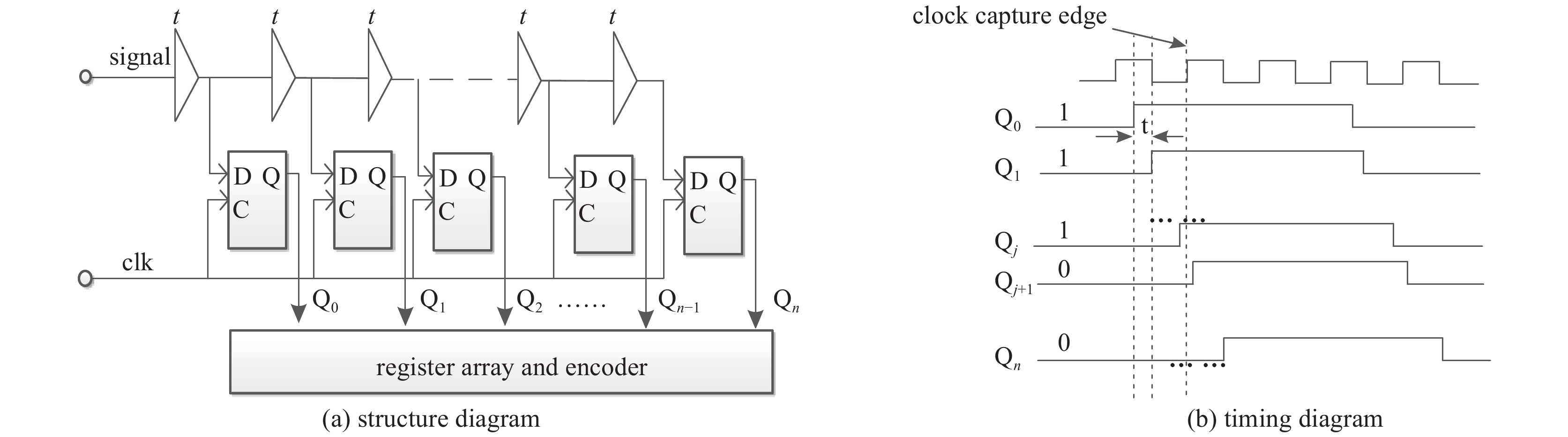

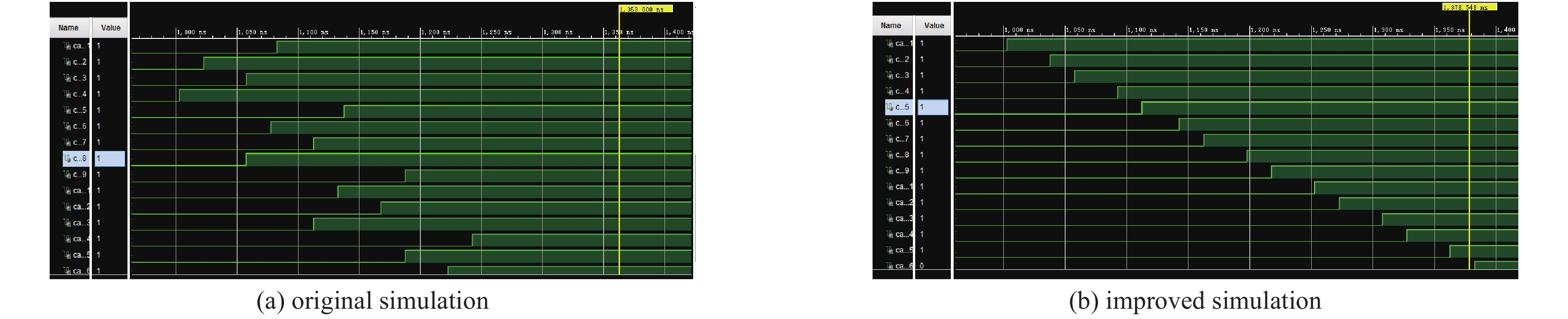

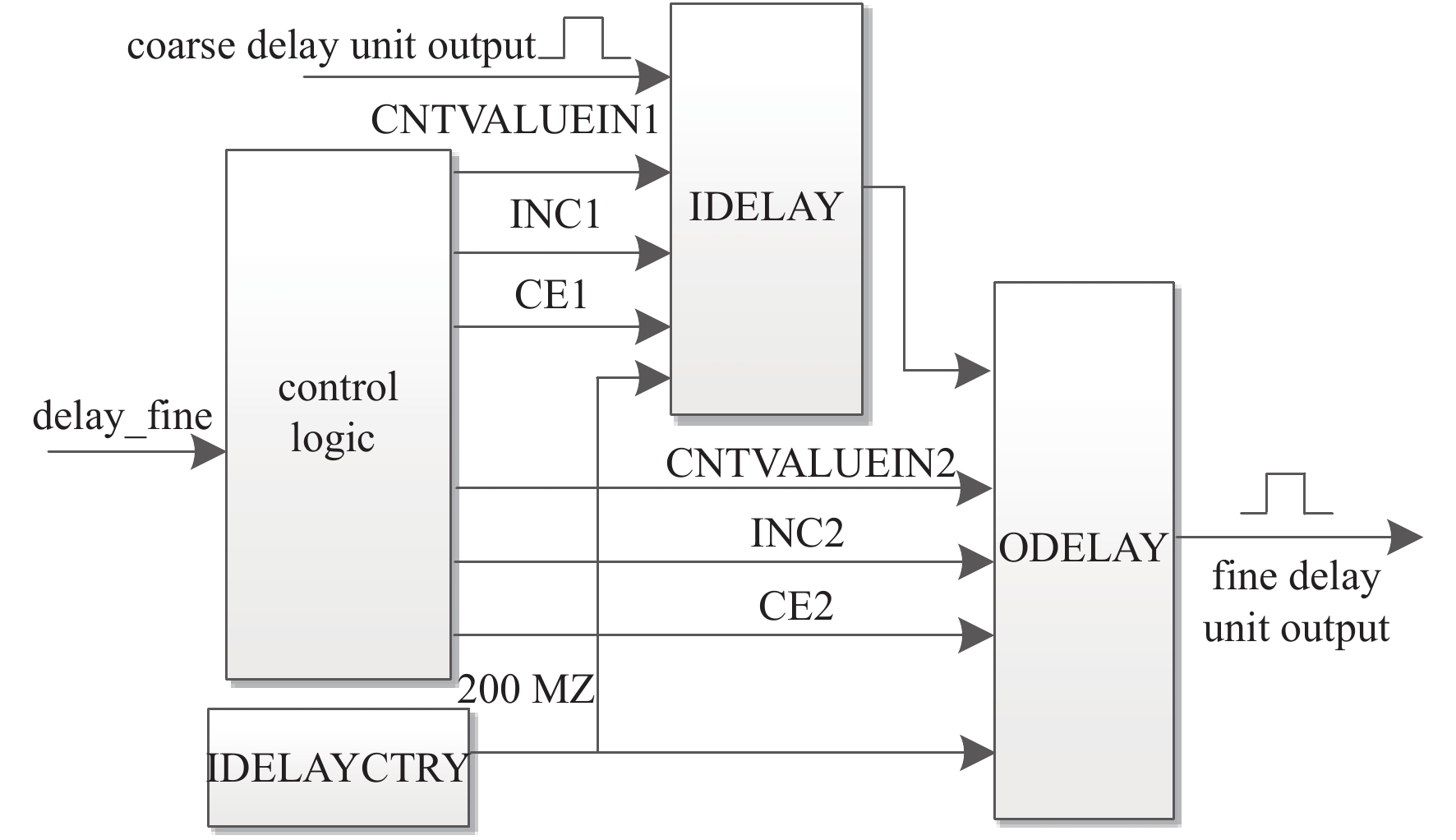

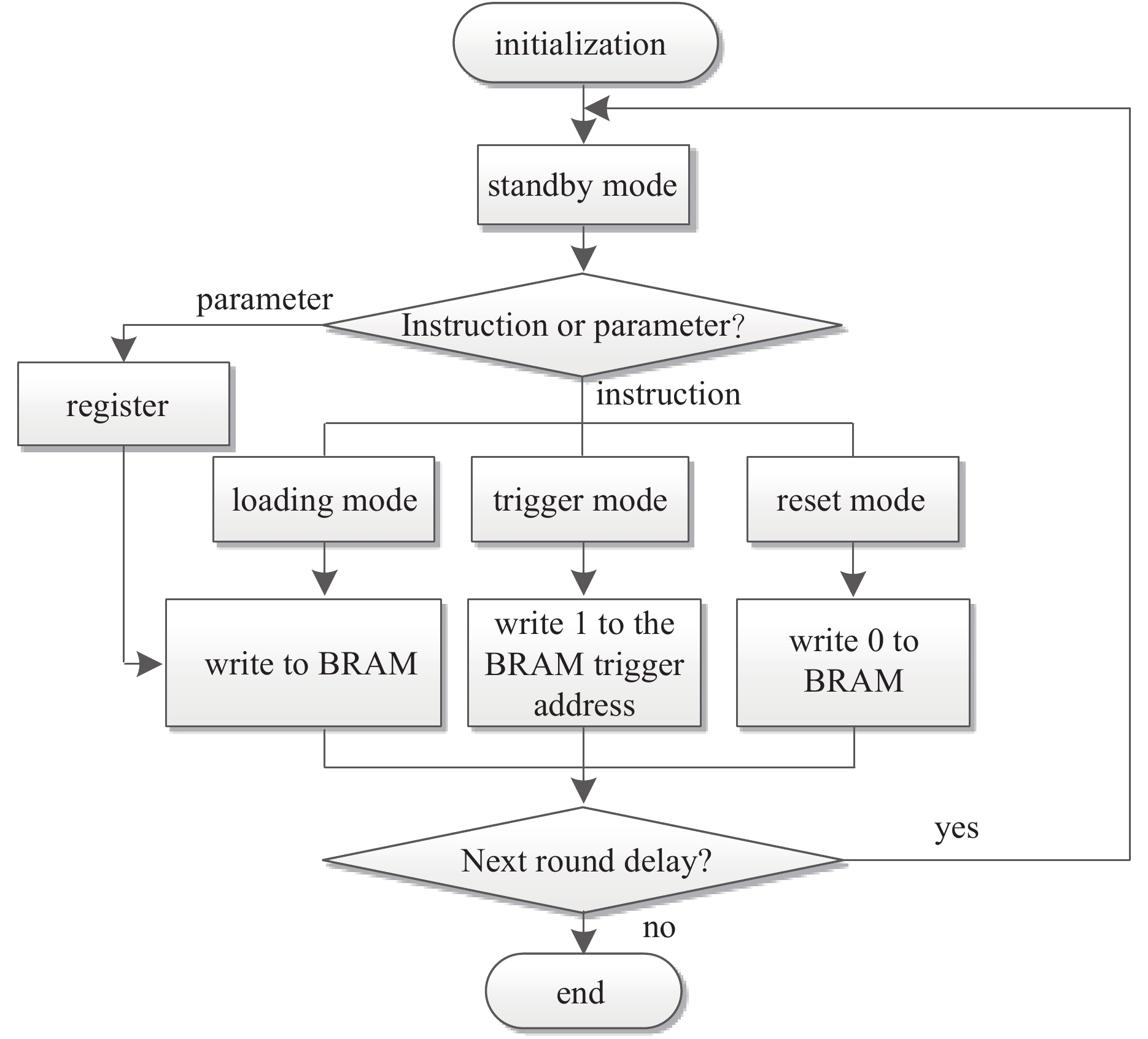

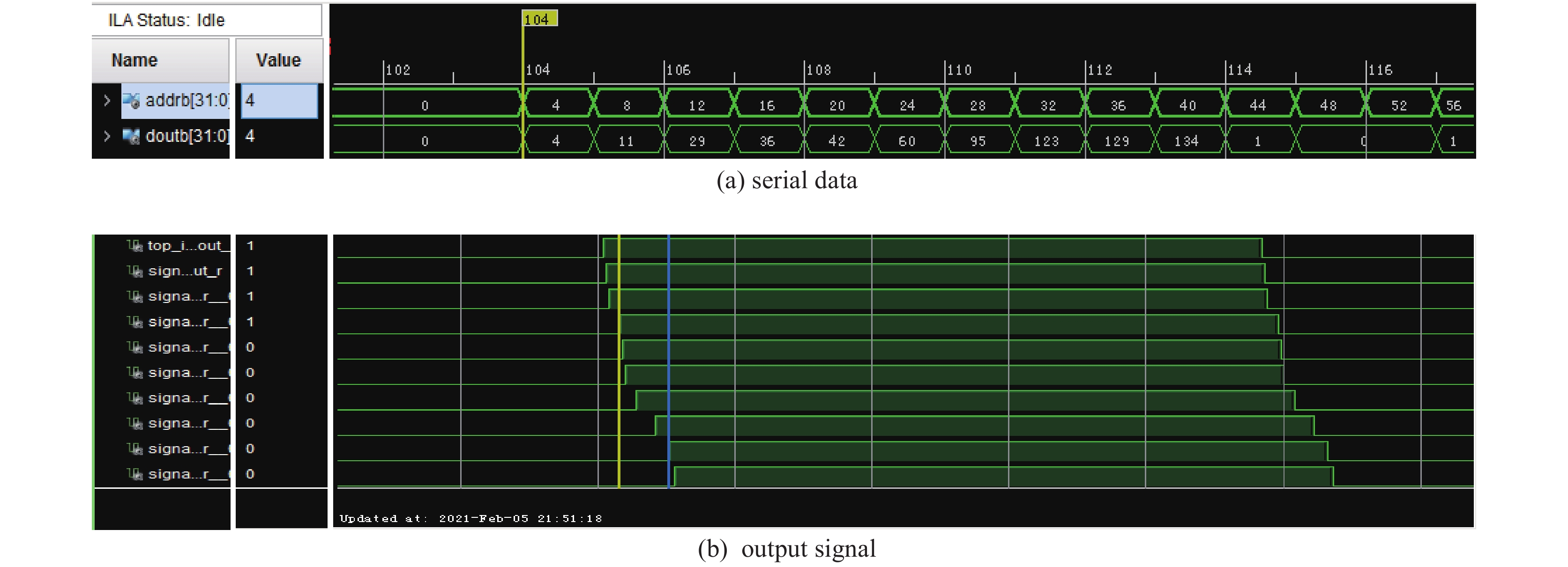

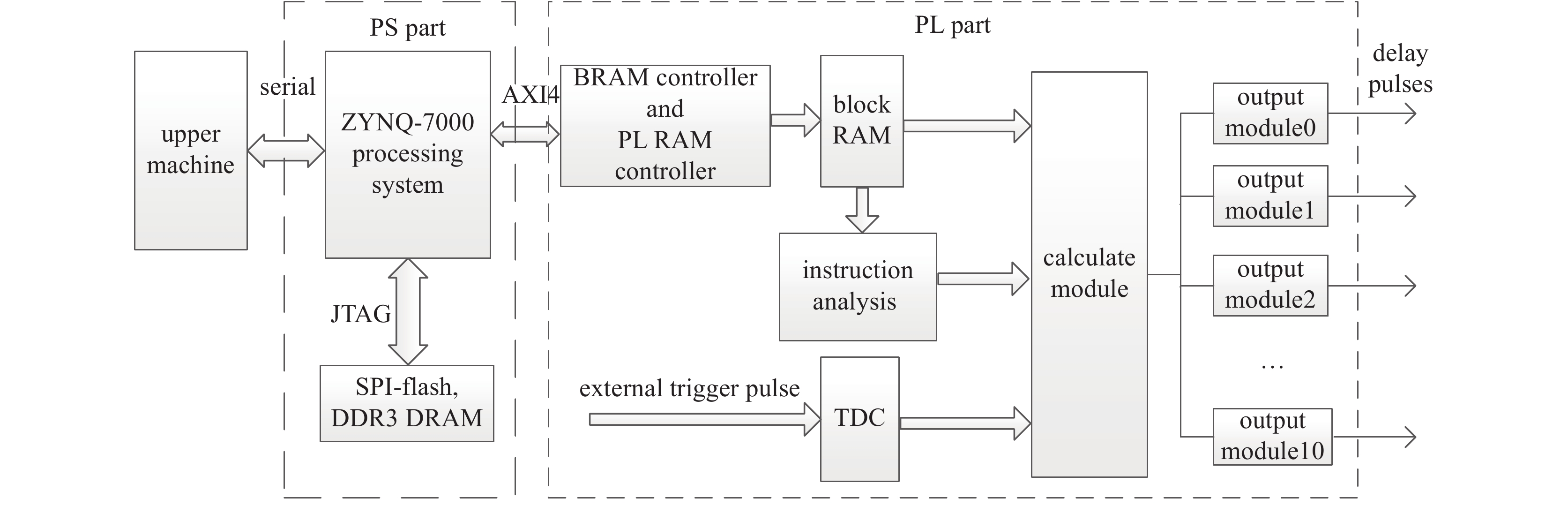

摘要: 针对全固态直线变压器驱动源(LTD)中大规模开关同步触发的需求,设计了一款基于ZYNQ-7000 SoC平台的全数字多路脉冲延时系统。介绍了该系统各功能模块,并重点从时间数字转换器(TDC)、多路脉冲输出及ARM核控制三个模块进行分析设计。详细阐述了TDC模块抽头延时法原理及高精度进位链的构造;采用粗延时和细延时结合设计多路脉冲输出模块,有效提高信号的延时精度和范围,且模块化设计提高了通道数目的可扩展性;阐述ARM核控制流程,实现了响应快、稳定性高的控制。最后对系统进行了仿真验证,固化后在器件上进行了实测。实验结果表明,系统能够对外部触发信号实现多路延时输出,信号脉冲宽度1200 ns,幅值1.8 V,延时步进1 ns,延时调节范围0~4.29 s,输出误差低于1 ns。Abstract: Aiming at the requirement of synchronous triggering of large-scale switches in the all-solid-state linear transformer drive source (LTD), this paper designs an all-digital multi-channel pulse delay system based on the ZYNQ-7000 SoC platform. The paper introduces the functional modules of the system, and focuses on the analysis and design of three modules: time-to-digital converter (TDC), multi-channel pulse output and ARM core control. First of all, it elaborates on the principle of the tap delay method of the TDC module and the structure of the high-precision carry chain; Secondly, it uses a combination of coarse delay and fine delay to design a multi-channel pulse output module, which effectively improves the delay accuracy and range of the signal. The modular design also improves the scalability of the number of channels. This paper also describes the control flow of the ARM core, which realizes the control with fast response and high stability. Finally, the paper presents the simulation verification of the system and measurement of the cured device. The measurement results show that the system can achieve multiple delay outputs for external trigger signals. The system output signal pulse width is 1200 ns, with 1.8 V amplitude, and the delay step is 1 ns, the delay adjustment range is 0~4.29 s. The system output signal error is less than 1 ns.

-

表 1 不同延时参数输出测试结果

Table 1. Results of different delay parameters output

channel No. delay parameter 0/ns delay parameter 25/ns delay parameter 100/ns delay parameter 200/ns 1 0.300 25.779 100.141 199.944 2 0.200 24.900 100.000 199.600 3 0.453 25.065 100.381 200.138 4 0.362 25.344 100.413 200.432 5 −0.119 25.208 100.167 199.344 6 −0.132 25.071 99.577 199.656 7 0.018 25.476 99.642 199.970 8 0.079 25.361 99.842 199.837 9 0.201 25.074 100.097 200.451 10 −0.489 24.451 99.679 199.377 -

[1] 刘锡三. 高功率脉冲技术[M]. 北京: 国防工业出版社, 2005: 410-411.Liu Xisan. High power pulse technology. Beijing: National Defense Industry Press, 2005: 410-411 [2] Ju W B, Dong W Y, Geun H R, et al. Solid state Marx generator using series-connected IGBTs[J]. IEEE Transactions on Plasma Science, 2005, 33(4): 1198-1204. doi: 10.1109/TPS.2005.852409 [3] 朱晓光, 张政权, 刘庆想, 等. 脉冲功率应用的IGBT快速驱动电路[J]. 强激光与粒子束, 2018, 30:015001. (Zhu Xiaoguang, Zhang Zhengquan, Liu Qingxiang, et al. High speed IGBT gate driving circuit applied to pulsed power system[J]. High Power Laser and Particle Beams, 2018, 30: 015001 doi: 10.11884/HPLPB201830.170330 [4] 李军, 虎雷, 李永明, 等. 一种高精度可延时同步脉冲产生系统[J]. 数字技术与应用, 2018, 36(7):182-184. (Li Jun, Hu Lei, Li Yongming, et al. A high-precision and time-delayable synchronous pulse generating system[J]. Digital Technology and Application, 2018, 36(7): 182-184 [5] 王梦宇, 张延超, 李美伦, 等. 用于激光雷达的高精度脉冲延时及脉宽控制研究[J]. 机械与电子, 2016, 34(8):3-6. (Wang Mengyu, Zhang Yanchao, Li Meilun, et al. Research on high precision pulse delay and pulse width control for lidar[J]. Machinery & Electronics, 2016, 34(8): 3-6 doi: 10.3969/j.issn.1001-2257.2016.08.001 [6] 陈伯俊, 周俊敏, 马军勇. 基于FPGA的高精度多路同步脉冲产生系统研究[J]. 科学技术与工程, 2010, 10(19):4793-4796. (Chen Bojun, Zhou Junmin, Ma Junyong. Research on high-precision multi-channel synchronous pulse generation system based on FPGA[J]. Science Technology and Engineering, 2010, 10(19): 4793-4796 doi: 10.3969/j.issn.1671-1815.2010.19.046 [7] 刘鹏, 许可. 一种基于FPGA的高精度大动态数字延迟单元的设计[J]. 微计算机信息, 2010, 26(8):132-134. (Liu Peng, Xu Ke. A design of high precision and large dynamic digital delay unit based on FPGA[J]. Microcomputer information, 2010, 26(8): 132-134 doi: 10.3969/j.issn.2095-6835.2010.08.055 [8] 俞帆, 张伟欣. FPGA设计中的跨时钟域问题[J]. 现代电子技术, 2014, 37(7):151-153, 156. (Yu Fan, Zhang Weixin. Cross-clock domain issues in FPGA design[J]. Modern Electronics Technique, 2014, 37(7): 151-153, 156 doi: 10.3969/j.issn.1004-373X.2014.07.044 [9] 王晓婷. 跨时钟域设计方法研究[D]. 西安: 西安电子科技大学, 2012: 12-13.Wang Xiaoting. Research on cross-clock domain design method. Xi’an: Xidian University, 2012: 12-13 [10] 罗敏, 宫月红, 喻明艳. 时间-数字转换器研究综述[J]. 微电子学, 2014, 44(3):372-376. (Luo Min, Gong Yuehong, Yu Mingyan. Research summary of time-to-digital converter[J]. Microelectronics, 2014, 44(3): 372-376 [11] Rashidzadeh R, Ahmadi M, Miller W C, et al. An all-digital self-calibration method for a vernier-based time-to-digital converter[J]. IEEE Transactions on Instrumentation and Measurement, 2010, 59(2): 463-469. doi: 10.1109/TIM.2009.2024699 [12] 章婷. 应用于NB-IoT全数字锁相环的时间数字转换器设计[D]. 南京: 东南大学, 2019: 23-26.Zhang Ting. Design of time-to-digital converter applied to NB-IoT all-digital phase-locked loop. Nanjing: Southeast University, 2019: 23-26 [13] 刘音华, 刘正阳, 刘琼瑶, 等. FPGA进位链实现TDC的若干关键技术问题[J]. 电子测量技术, 2018, 41(14):122-127. (Liu Yinhua, Liu Zhengyang, Liu Qiongyao, et al. Some key technical problems of FPGA carry chain to realize TDC[J]. Electronic Measurement Technology, 2018, 41(14): 122-127 -

下载:

下载: