| [1] |

Kim K, Iliadis A A. Operational upsets and critical new bit errors in CMOS digital inverters due to high power pulsed electromagnetic interference[J]. Solid-State Electronics, 2010, 54(1): 18-21. doi: 10.1016/j.sse.2009.09.006

|

| [2] |

Iliadis A A, Kim K. Theoretical foundation for upsets in CMOS circuit due to high-power electromagnetic interference[J]. IEEE Trans Device Mater Reliab, 2010, 10(3): 347-352. doi: 10.1109/TDMR.2010.2050692

|

| [3] |

Chai Changchun, Xi Xiaowen, Ren Xingrong, et al. The damage effect and mechanism of the bipolar transistor induced by the intense electromagnetic pulse[J]. Acta Physica Sinica, 2010, 59(11): 8118-8124. doi: 10.7498/aps.59.8118

|

| [4] |

Wang Haiyang, Li Jiayin, Li Hao, et al. Experimental study and SPICE simulation of CMOS inverters latch-up effects due to high power microwave interference[J]. Prog Electromagn Res, 2008, 87: 313-330. doi: 10.2528/PIER08100408

|

| [5] |

Mansson D, Thottappillil R, Backstrom M, et al. Susceptibility of civilian GPS receivers to electromagnetic radiation[J]. IEEE Trans Electromagn Compat, 2008, 50(1): 434-437.

|

| [6] |

You Hailong, Lan Jianchun, Fan Juping, et al. Research on characteristics degradation of n-metal-oxide-semiconductor field-effect transistor induced by hot carrier effect due to high power microwave[J]. Acta Physica Sinica, 2012, 61: 108501. doi: 10.7498/aps.61.108501

|

| [7] |

Backstrom M G, Lovstrand K G. Susceptibility of electronic systems to high-power microwave: summary of test experience[J]. IEEE Trans Electromagn Compat, 2004, 46(3): 396-403. doi: 10.1109/TEMC.2004.831814

|

| [8] |

Nitsch D, Camp M, Sabath F, et al. Susceptibility of some electronic equipment to HPEM threats[J]. IEEE Trans Electromagn Compat, 2004, 46(3): 380-387. doi: 10.1109/TEMC.2004.831842

|

| [9] |

Vault W L. The damage susceptibility of integrated circuits to a simulated IEMP transient[J]. IEEE Transactions on Nuclear Science, 1973, 20(6): 40-47. doi: 10.1109/TNS.1973.4327371

|

| [10] |

Kim K, Iliadis A A. Granatstein V L. Effects of microwave interference on the operational parameters of n-channel enhancement mode MOSFET devices in CMOS integrated circuits[J]. Solid-State Electronics, 2004, 48(10/11): 1795-1799. doi: 10.1016/j.sse.2004.05.015

|

| [11] |

Kim K, Iliadis A A. Critical upsets of CMOS inverters in static operation due to high-power microwave interference[J]. IEEE Transactions on Electromagnetic Compatibility, 2007, 49(4): 876-885. doi: 10.1109/TEMC.2007.908820

|

| [12] |

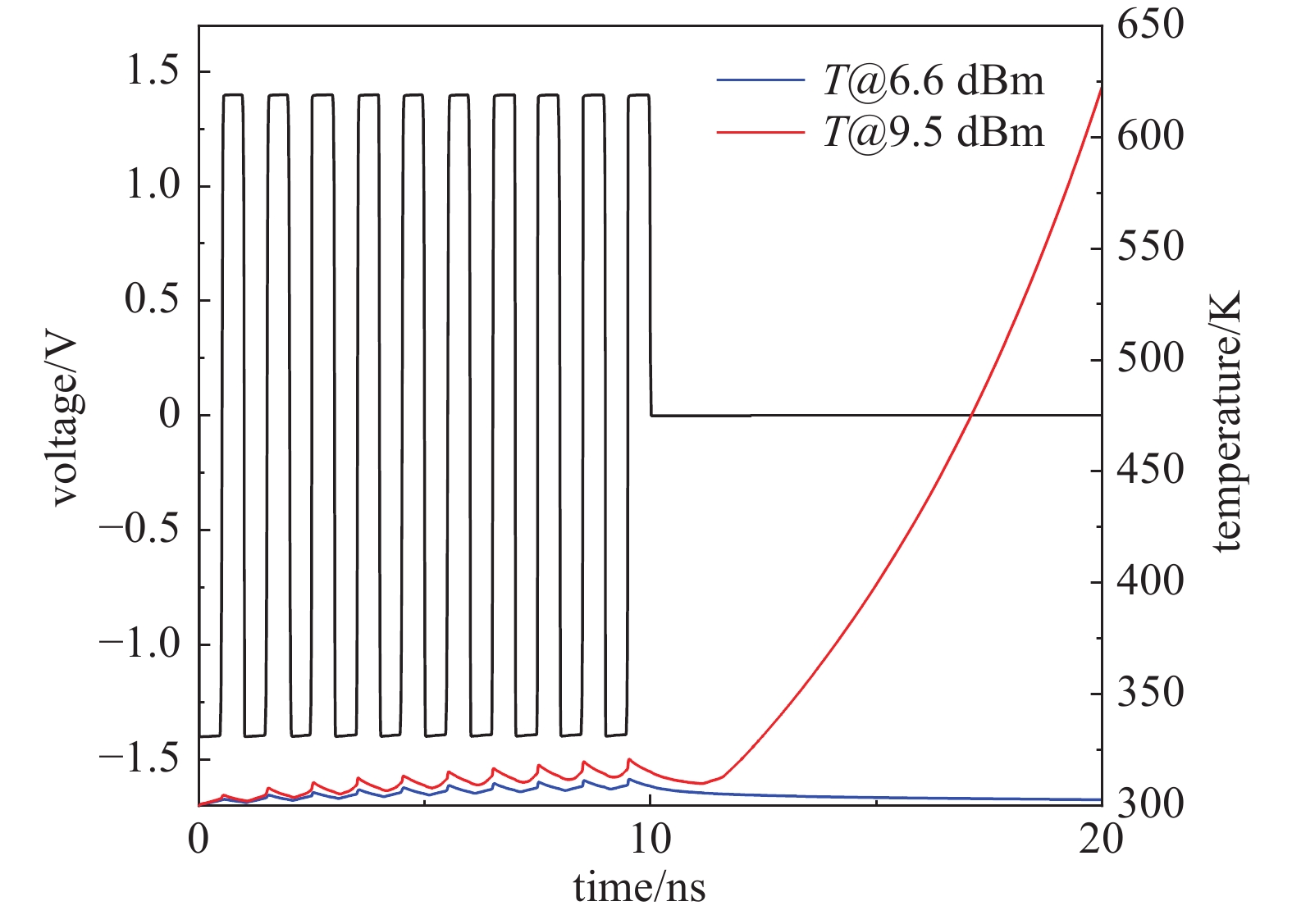

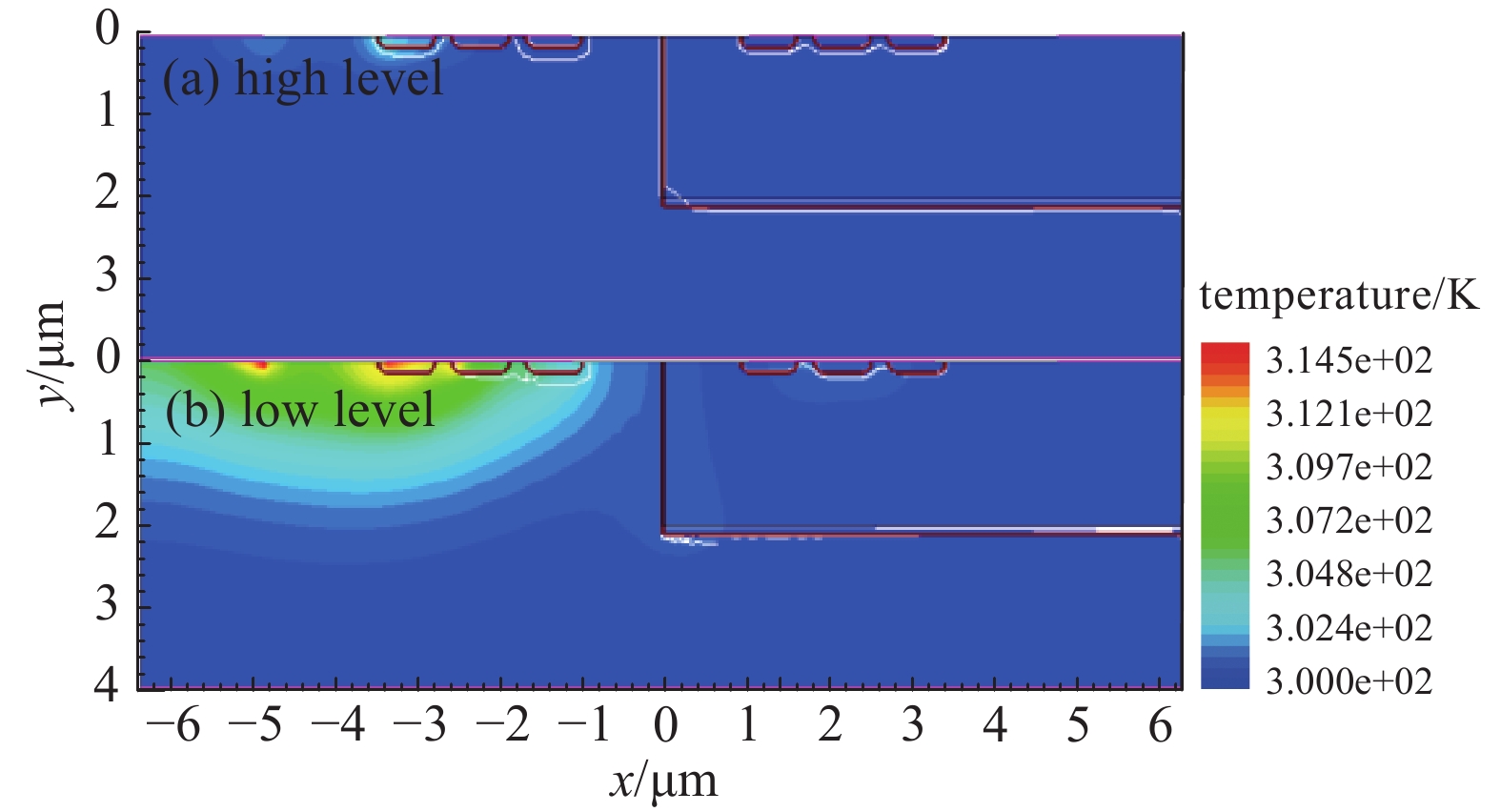

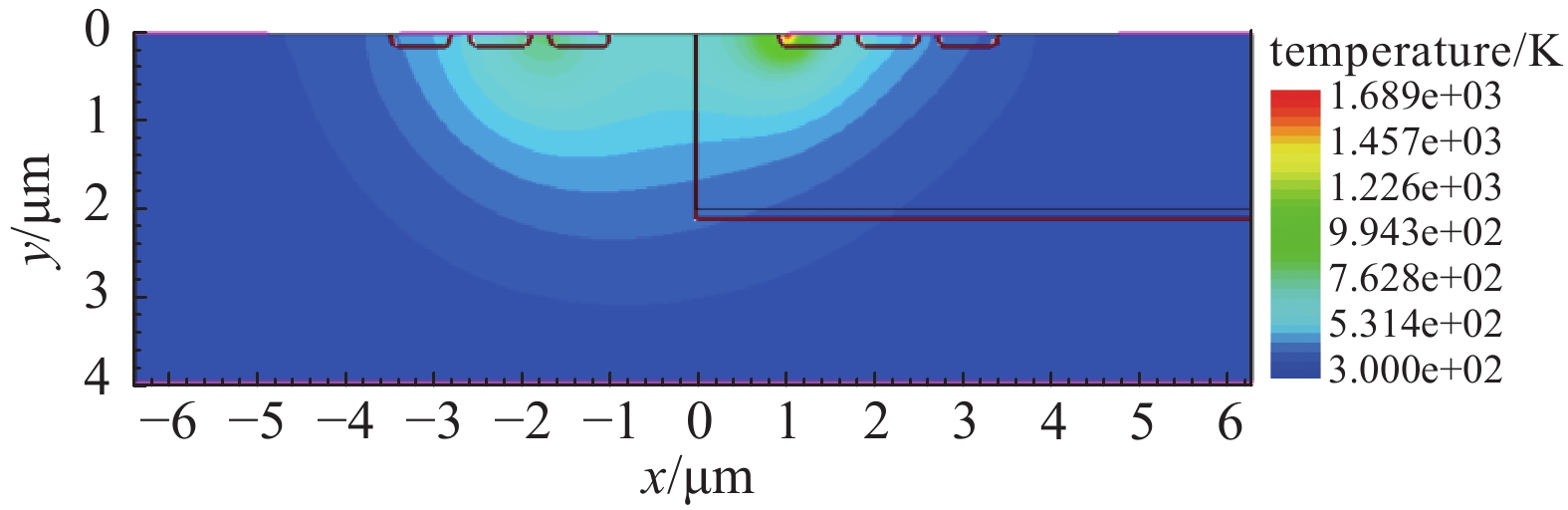

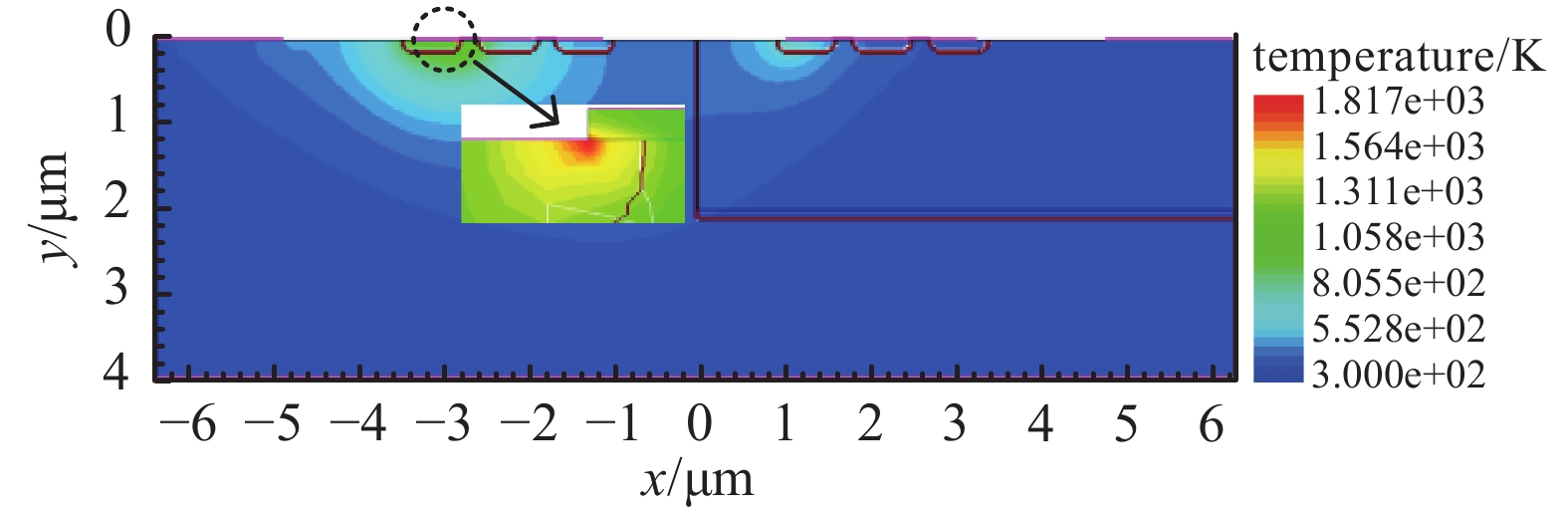

Yu X H, Chai C C, Ren X R, et al. Temperature dependence of latch-up effects in CMOS inverter induced by high power microwave[J]. J Semicond, 2014, 35(8): 115-120.

|

| [13] |

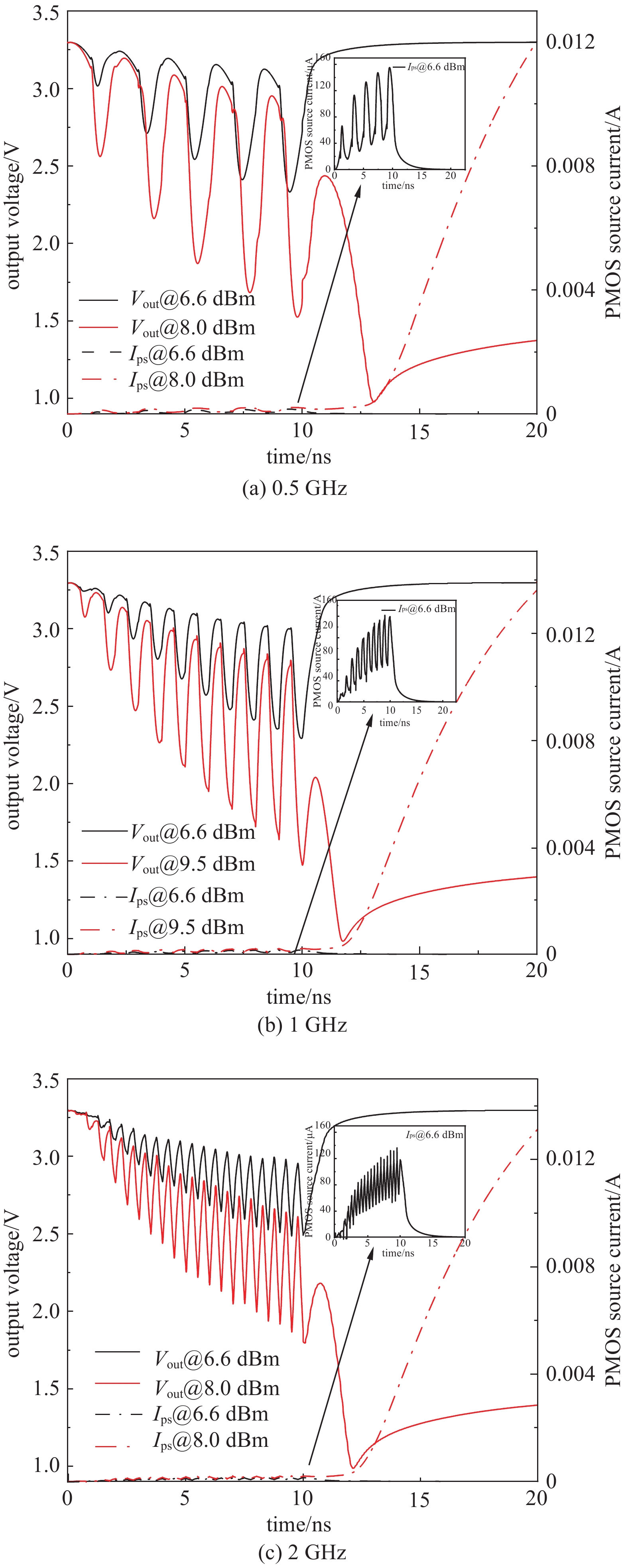

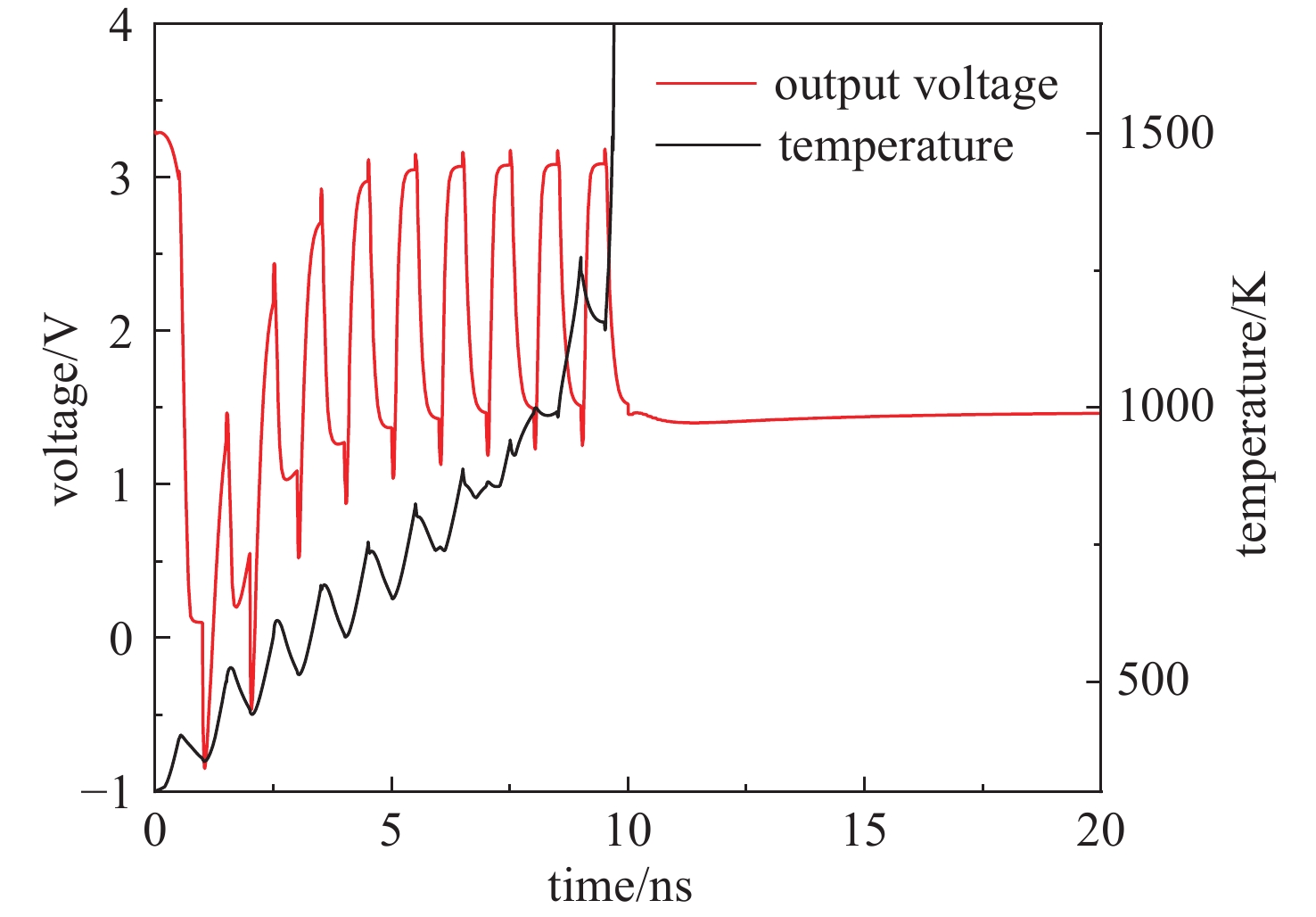

Yu X H, Chai C C, Liu Y, et al. Modeling and understanding of the frequency dependent HPM upset susceptibility of the CMOS inverter[J]. China Inform Sci, 2015, 58(8): 1-11.

|

| [14] |

Yu X H, Chai C C, Qiao L P, et al. Modeling and analysis of the HPM pulse-width upset effect on CMOS inverter[J]. J Semicond, 2015, 36(5): 66-71.

|

| [15] |

2004 ISE-TCAD Dessis simulation user’s manual[M]. Zurich: Integrated Systems Engineering Corp, 2004.

|

| [16] |

Donoval D, Vrbicky A, Marek J, et al. Evaluation of the ruggedness of power DMOS transistor from electro-thermal simulation of UIS behavior[J]. Solid-State Electronics, 2008, 52(6): 892-898.

|

| [17] |

TEXAS INSTRUMENTS. SN74LVC1G00 Single 2-input positive-NAND gate [EB/OL]. https://www.ti.com/cn/lit/d s/symlink/sn74lvc1g00.pdf?ts=1630386223722

|

| [18] |

Tasca D M. Pulse power failure modes in semiconductors[J]. IEEE Transactions on Nuclear Science, 1970, 17(6): 364-372.

|

| [19] |

Brown W D. Semiconductor device degradation by high amplitude current pulses[J]. IEEE Transactions on Nuclear Science, 1972, 19(6): 68-75.

|

| [20] |

Jenkins C R, Durgin D L. EMP susceptibility of integrated circuits[J]. IEEE Transactions on Nuclear Science, 1975, 22(6): 2494-2499.

|

下载:

下载: