Electromagnetic susceptibility analysis of FPGA based on conducted coupling of power supply network

-

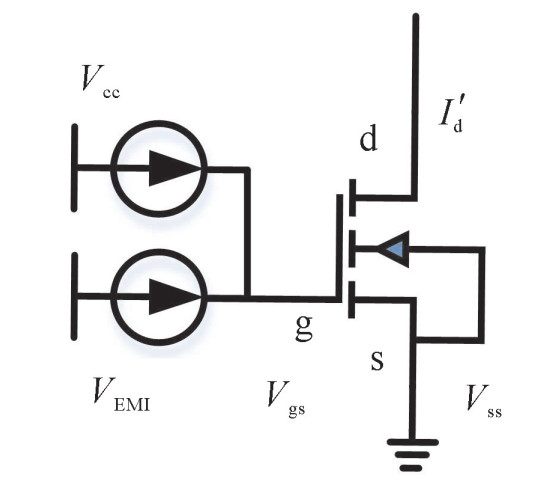

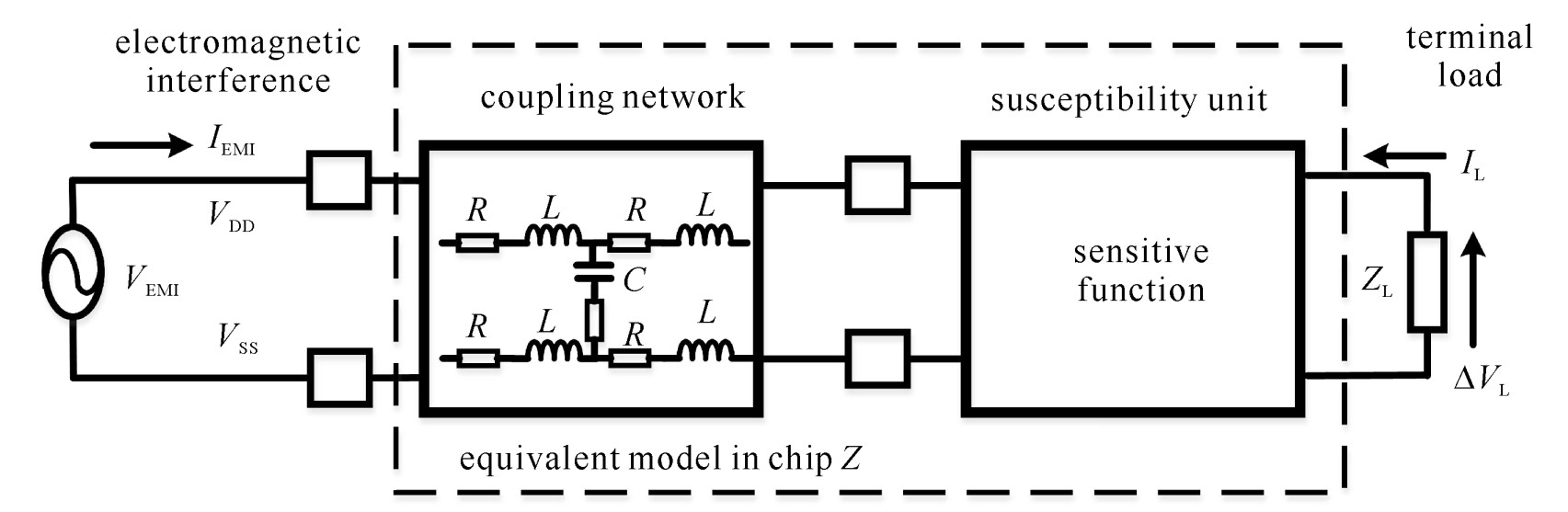

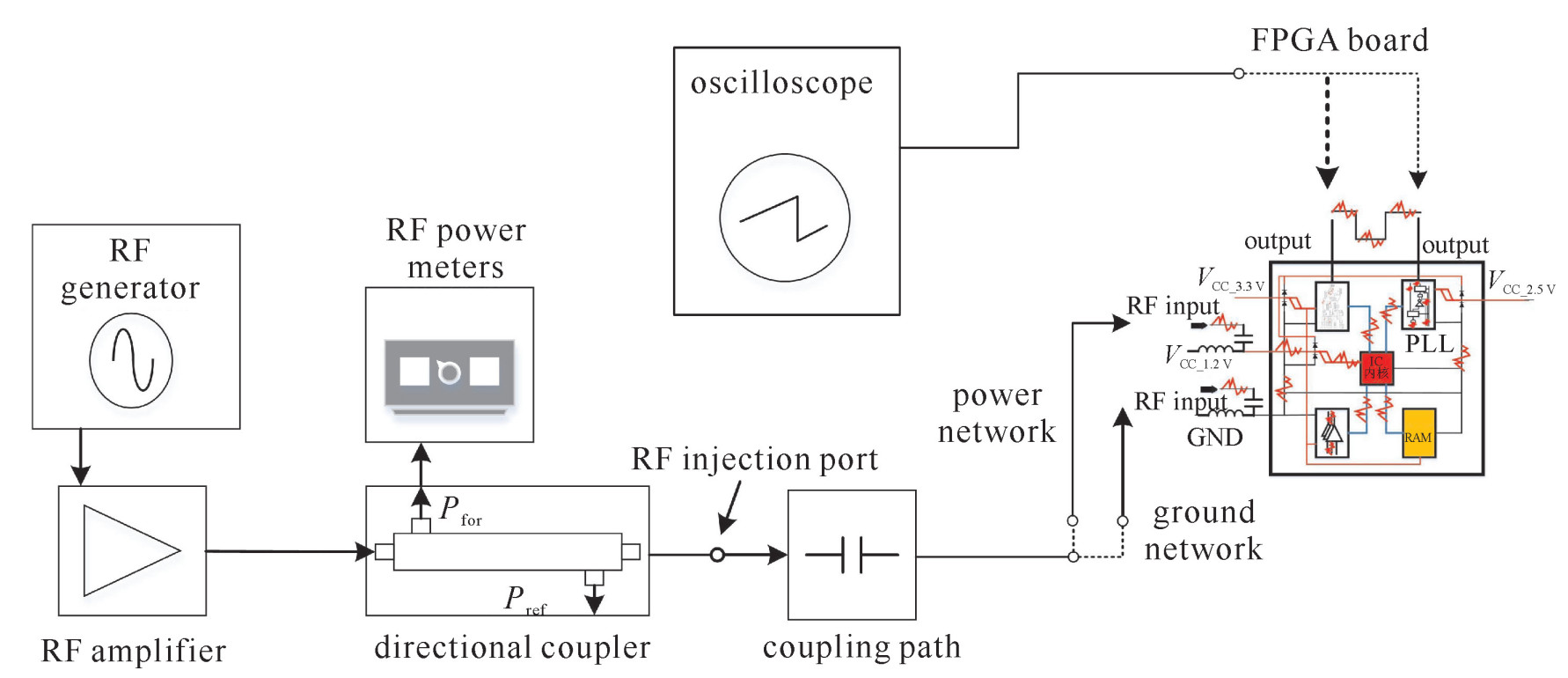

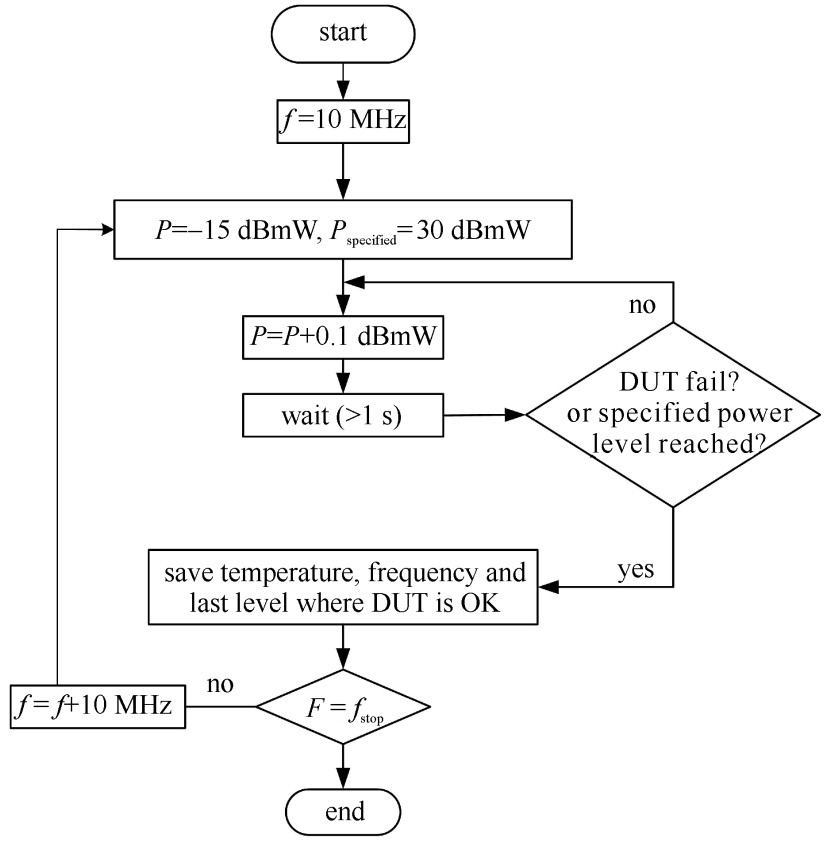

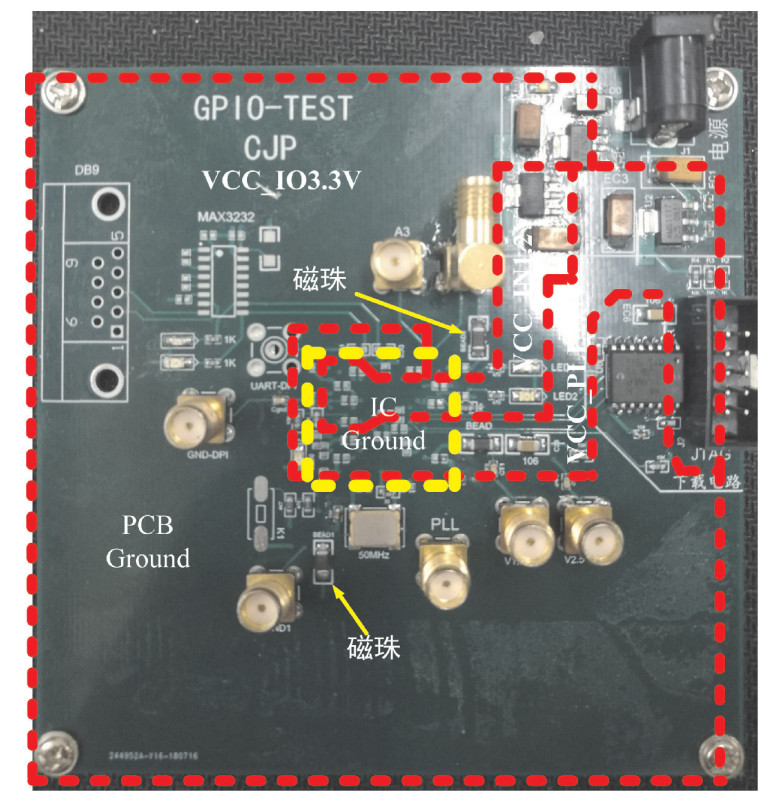

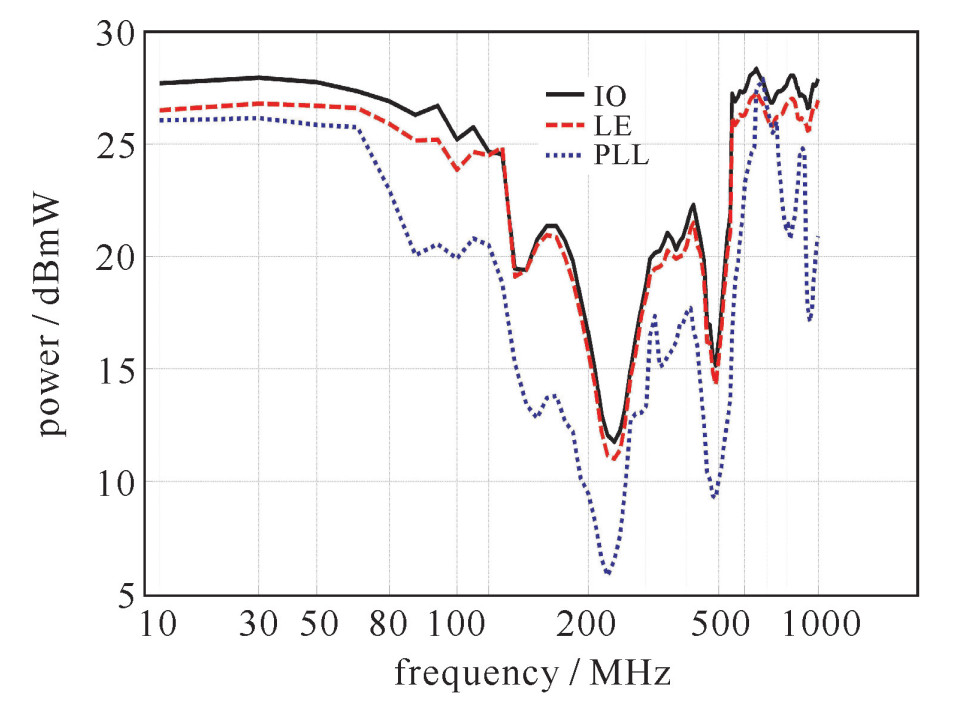

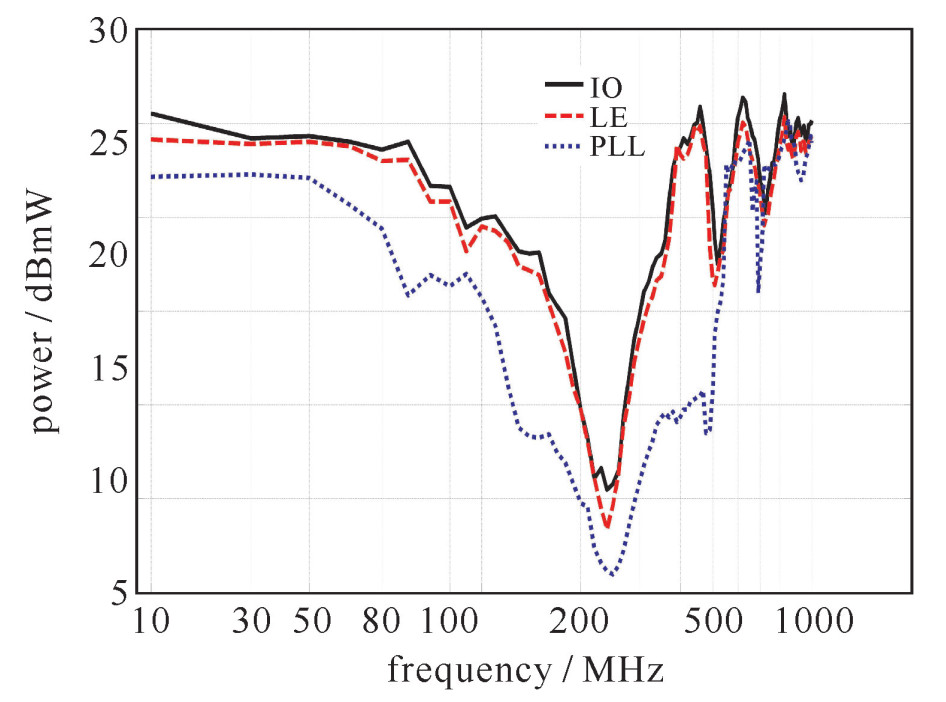

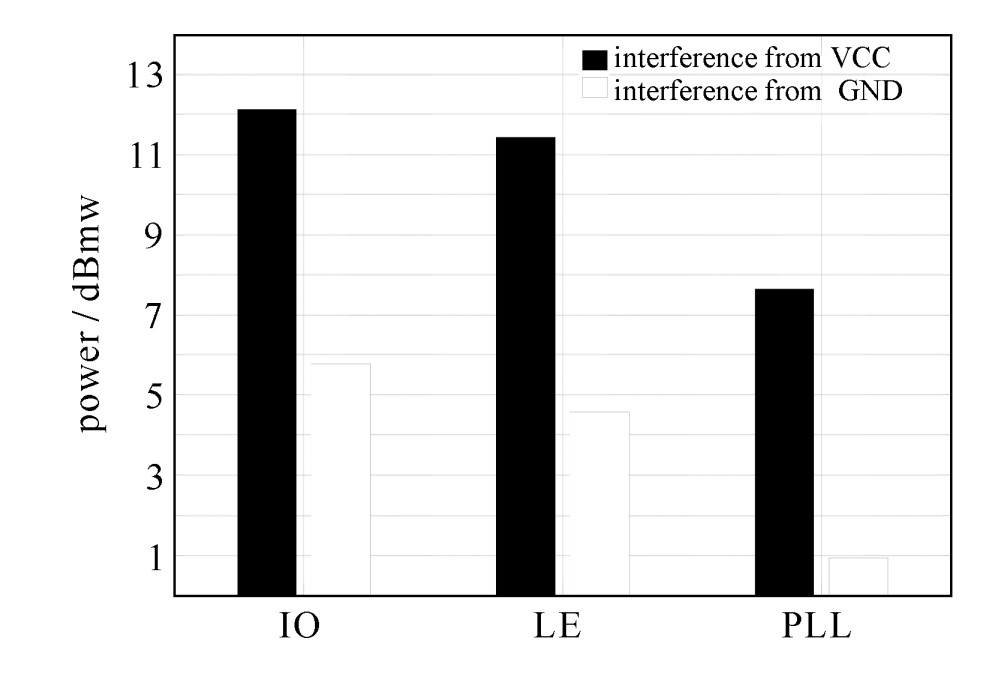

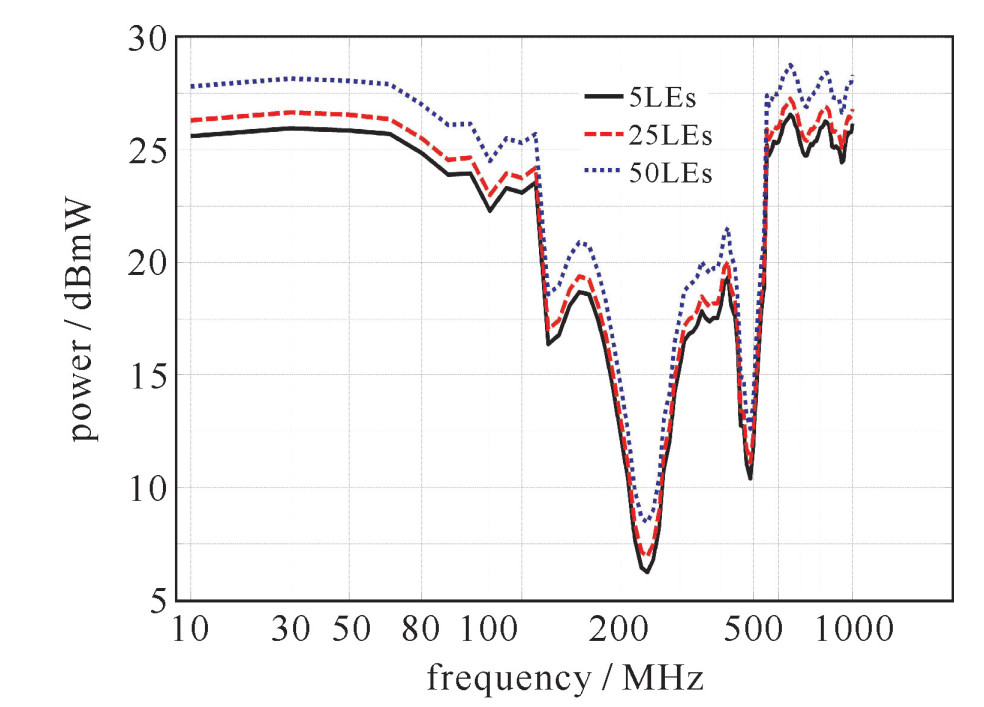

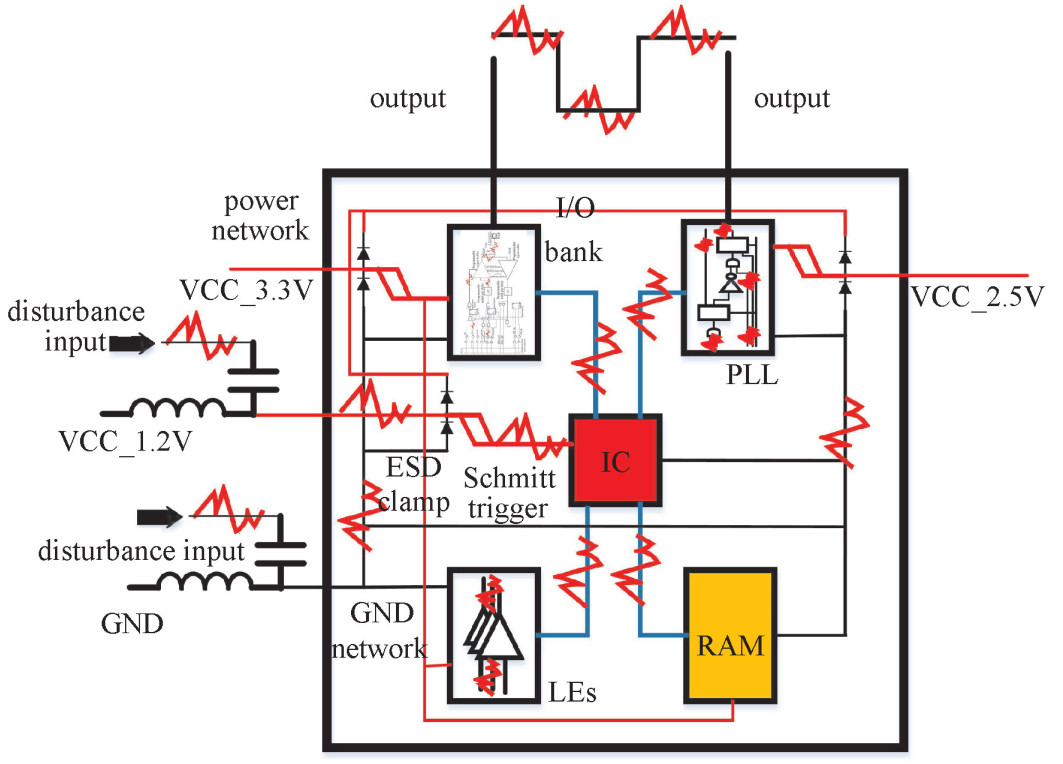

摘要: 针对电磁干扰(EMI)导致电子系统关键功能单元行为失效或安全问题,研究基于供电网络传导耦合的核心可编程集成电路(IC)电磁敏感(EMS)特性。分析典型FPGA供电网络的拓扑结构及其EMI传导耦合机理,设计基于EMI直接功率注入法的敏感度测试平台,测试受试芯片供电网络EMI传导耦合时典型功能单元的EMS特性,获取输入输出端口(IO)、逻辑单元(LE)、内部锁相环电路(PLL)等功能单元的敏感度阈值,给出LE冗余设计对相应电路EMS特性的影响规律。结果表明,在10 MHz~1 GHz干扰频率范围内,供电网络EMI敏感度由高到低依次为PLL,LE,IO,且IC地网络EMI敏感度高2~7 dBmW,LE冗余设计能有效改善逻辑功能单元电磁敏感度。Abstract: Due to the problem of behavior failure or functional safety for electronic system caused by electromagnetic interference (EMI), the electromagnetic susceptibility characteristics of programmable integrated circuit (IC) based on the conducted coupling of power supply network are studied. The topology structure of power supply network and the EMI conducted coupling mechanism of typical FPGA are analyzed, and the immunity test platform based on EMI direct power injection method is designed. The electromagnetic susceptibility feature of typical functional units are measured when the EMI is conducted to the power supply network of the IC under test, then the susceptibility thresholds of internal phase-locked loop (PLL) circuit, logic element (LE) and input/output port is obtained and the influence law of LE redundancy design on EMS characteristic of corresponding circuits is given. The results show that, for interference frequencies in the range of 10 MHz-1 GHz, functional units with EMI susceptibility from high to low are PLL, LE and IO, and the EMI susceptibility of IC ground network is 2-7 dBmW higher. LE redundancy design can effectively improve the EMS of logical functional units.

-

表 1 功能模块工作电压

Table 1. Working voltage of functional module

functional module working voltage/V I/O port 3.3 logic elements 3.3 embedded memory 3.3 PLL 2.5 chip core 1.2 表 2 片内单元测试功能

Table 2. Functional units in the chip

unit in the chip PLL logic element(number of usage) IO port 5 LEs 20 LEs 50 LEs logic function output 1 kHz square wave four-bit counter four-bit counter four-bit counter input 1 kHz square wave

output 1 kHz square wave表 3 冗余电路LE使用数量与敏感特性变化

Table 3. Number of LE used in redundant circuits and the change of susceptibility

functional circuit number of LES used susceptibility improvement/dBm 5 0 four-bit counter 25 +0.54 50 +1.76 -

[1] 黎明, 黄如. 后摩尔时代大规模集成电路器件与集成技术[J]. 中国科学: 信息科学, 2018, 4808: 963-977. https://www.cnki.com.cn/Article/CJFDTOTAL-PZKX201808001.htmLi Ming, Huang Ru. Device and integration technologies for VLSI in post-Moore era. Scientia Sinica: Informationis, 2018, 4808: 963-977 https://www.cnki.com.cn/Article/CJFDTOTAL-PZKX201808001.htm [2] Lim J, Cho J, Jung D H, et al. Modeling and analysis of TSV noise coupling effects on RF LC-VCO and shielding structures in 3D IC[J]. IEEE Trans on Electromagnetic Compatibility, 2018, 60(6): 1939-1947. doi: 10.1109/TEMC.2018.2800120 [3] 陈选龙, 杨妙林, 李洁森, 等. 集成电路氧化层失效定位技术研究[J]. 微电子学, 2018, 48(4): 560-564. https://www.cnki.com.cn/Article/CJFDTOTAL-MINI201804028.htmChen Xuanlong, Yang Miaolin, Li Jiesen, et al. Study on oxide defect localization technology of integrated circuit. Microelectronics, 2018, 48(4): 560-564 https://www.cnki.com.cn/Article/CJFDTOTAL-MINI201804028.htm [4] Shim Y, Dan O. System level modeling of timing margin loss due to dynamic supply noise for high-speed clock forwarding interface[J]. IEEE Trans on Electromagnetic Compatibility, 2016, 58(4): 1349-1358. doi: 10.1109/TEMC.2016.2574720 [5] Ghfiri C, Boyer A, Durier A, et al. A new methodology to build the internal activity block of ICEM-CE for complex integrated circuits[J]. IEEE Trans Electromagnetic Compatibility, 2018, 60(5): 1500-1509. doi: 10.1109/TEMC.2017.2767084 [6] 赵娟, 李波, 李玺钦, 等. 高电磁兼容性大功率恒流源设计与实现[J]. 强激光与粒子束, 2018, 30: 025007. doi: 10.11884/HPLPB201830.170359Zhao Juan, Li Bo, Li Xiqin, et al. Design and actualization of high electromagnetic compatibility high power constant-current supply. High Power Laser and Particle Beams, 2018, 30: 025007 doi: 10.11884/HPLPB201830.170359 [7] Zhou L, Zheng W S, Hua Y J, et al. Investigation on failure mechanisms of GaN HEMT caused by high-power microwave (HPM) pulses[J]. IEEE Trans Electromagnetic Compatibility, 2017, 59(3): 902-909. doi: 10.1109/TEMC.2016.2628046 [8] Kim H, Kim J, Fan J, et al. Precise analytical model of power supply induced jitter transfer function at inverter chains[J]. IEEE Trans Electromagnetic Compatibility, 2018, 60(5): 1491-1499. doi: 10.1109/TEMC.2017.2764867 [9] Zhou L, Chen X, Peng H L, et al. Experiments and comparisons of power to failure for SiGe-based low-noise amplifiers under high-power microwave pulses[J]. IEEE Trans Electromagnetic Compatibility, 2018, 60(5): 1427-1435. doi: 10.1109/TEMC.2017.2771252 [10] 王振义, 周长林, 余道杰, 等. 低压差线性稳压器电磁抗扰度测试与建模[J]. 强激光与粒子束, 2015, 27: 103211. doi: 10.11884/HPLPB201527.103211Wang Zhenyi, Zhou Changlin, Yu Daojie, et al. Immunity modeling and measurement of low-dropout linear regulator. High Power Laser and Particle Beams, 2015, 27: 103211 doi: 10.11884/HPLPB201527.103211 [11] 秦海潮, 阎照文, 苏东林, 等. 三维TSV集成电路电磁敏感性分析方法[J]. 北京航空航天大学学报, 2017, 43(12): 2406-2415. https://www.cnki.com.cn/Article/CJFDTOTAL-BJHK201712007.htmQin Haichao, Yan Zhaowen, Su Donglin, et al. Electromagnetic susceptibility analysis method for 3D TSV ICs. Journal of Beijing University of Aeronautics and Astronautics, 2017, 43(12): 2406-2415 https://www.cnki.com.cn/Article/CJFDTOTAL-BJHK201712007.htm [12] Ren L, Li T, Chandra S, et al. Prediction of power supply noise from switching activity in an FPGA[J]. IEEE Trans Electromagnetic Compatibility, 2014, 56(3): 699-706. doi: 10.1109/TEMC.2013.2293872 [13] Piersanti S, Paulis F D, Olivieri C, et al. Decoupling capacitors placement for a multichip PDN by a nature-inspired algorithm[J]. IEEE Trans Electromagnetic Compatibility, 2018, 60(6): 1678-1685. doi: 10.1109/TEMC.2017.2770089 [14] Mehri M, Masoumi N. Statistical prediction and quantification of radiated susceptibility for electronic systems PCB in electromagnetic polluted environments[J]. IEEE Trans Electromagnetic Compatibility, 2017, 59(2): 498-508. doi: 10.1109/TEMC.2016.2610463 [15] 陈放, 田建宇, 孙兆牛, 等. 基于信号完整性与电源完整性的PCB电磁兼容协同仿真方法研究[J]. 航天控制, 2017, 3504: 90-94. https://www.cnki.com.cn/Article/CJFDTOTAL-HTKZ201704017.htmChen Fang, Tian Jianyu, Sun Zhaoniu, et al. The research of EMC co-simulation method for PCB based on SI and PI. Aerospace Control, 2017, 3504: 90-94 https://www.cnki.com.cn/Article/CJFDTOTAL-HTKZ201704017.htm [16] Ayed A, Dubois T, Levant J L, et al. Failure mechanism study and immunity modeling of an embedded analog-to-digital converter based on immunity measurements[J]. Microelectronics Reliability, 2015, 55(9/10): 2067-2071. https://www.sciencedirect.com/science/article/pii/S0026271415300561 [17] 梁华国, 孙红云, 孙骏, 等. 一种基于FPGA的微处理器软错误敏感性分析方法[J]. 电子与信息学报, 2017, 39(1): 245-249. https://www.cnki.com.cn/Article/CJFDTOTAL-DZYX201701034.htmLiang Huaguo, Sun Hongyun, Sun Jun, et al. FPGA-based soft error sensitivity analysis method for microprocessor. Journal of Electronics & Information Technology, 2017, 39(1): 245-249 https://www.cnki.com.cn/Article/CJFDTOTAL-DZYX201701034.htm -

下载:

下载: