Failure mechanism of a kind of FPGA chip under RF interference

-

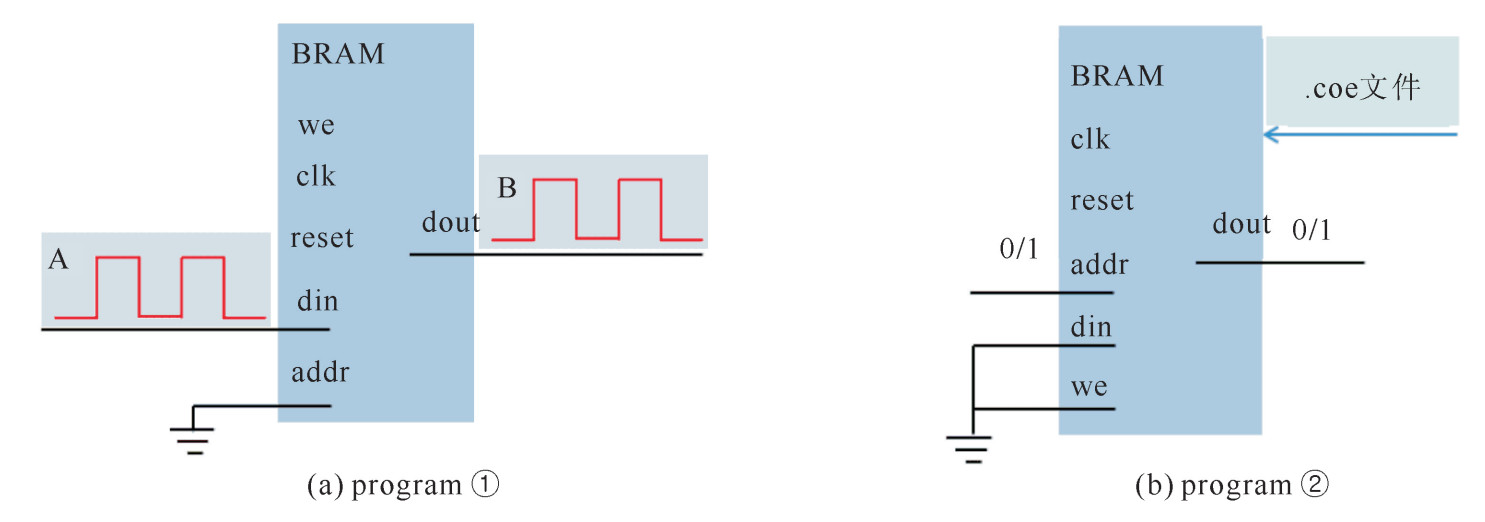

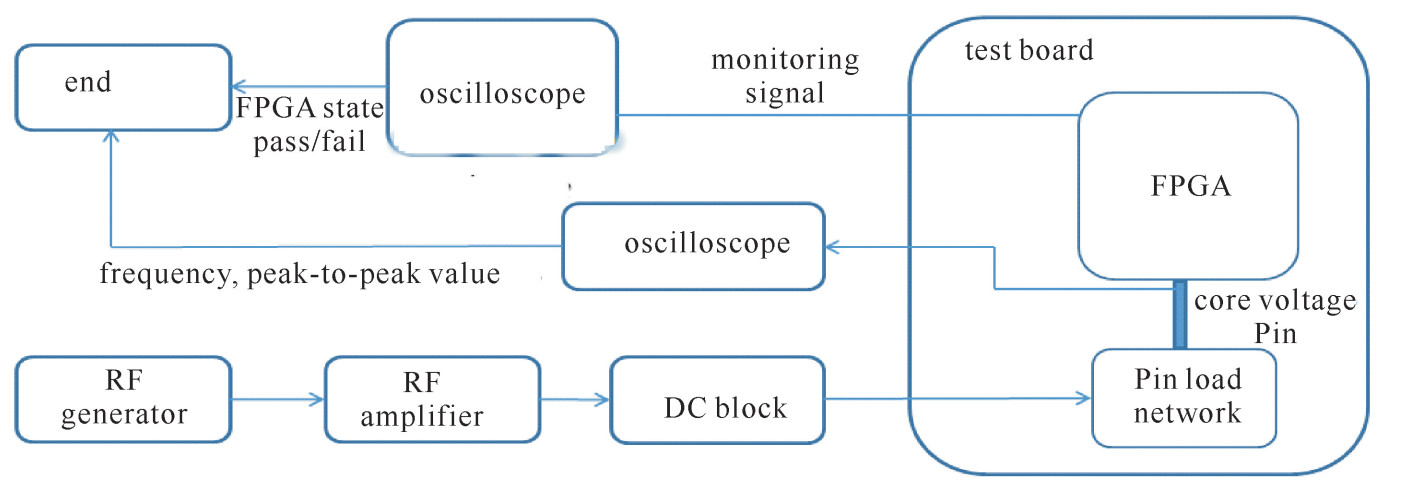

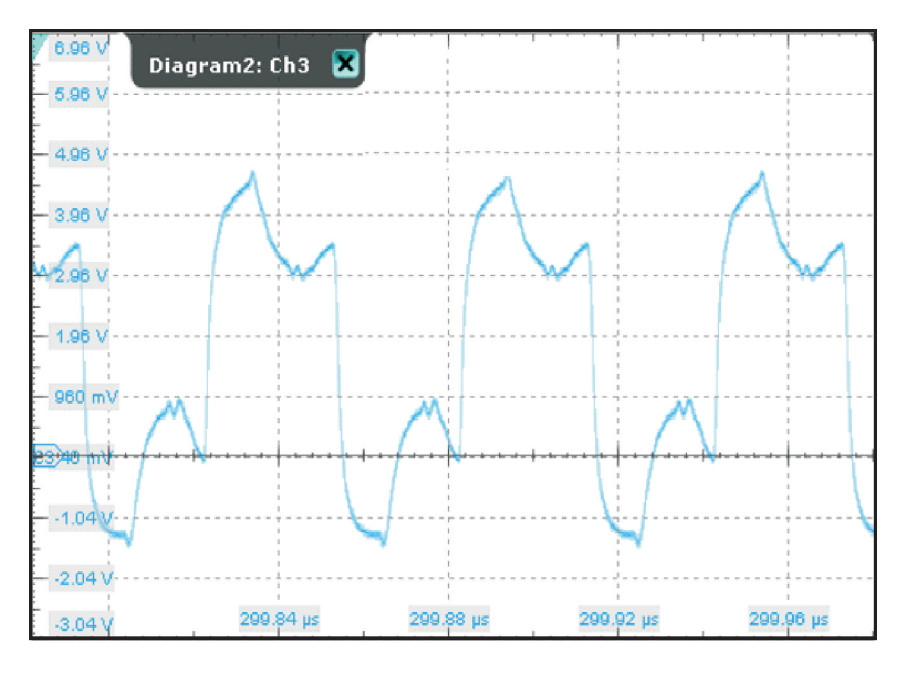

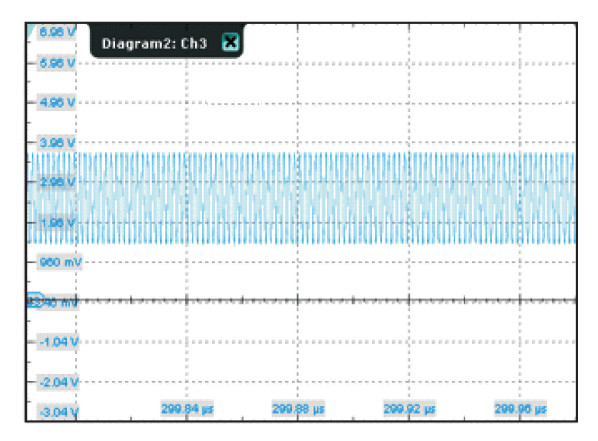

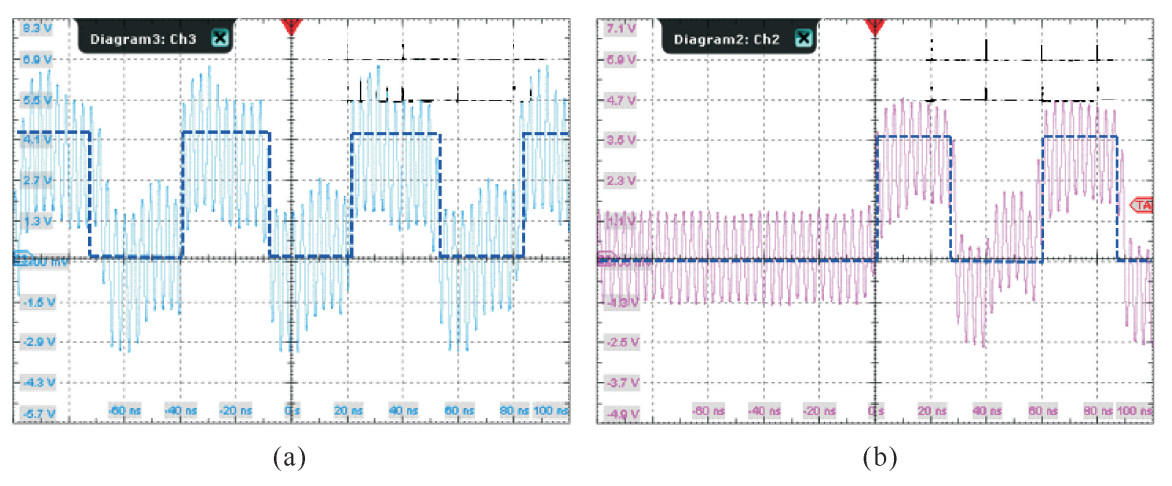

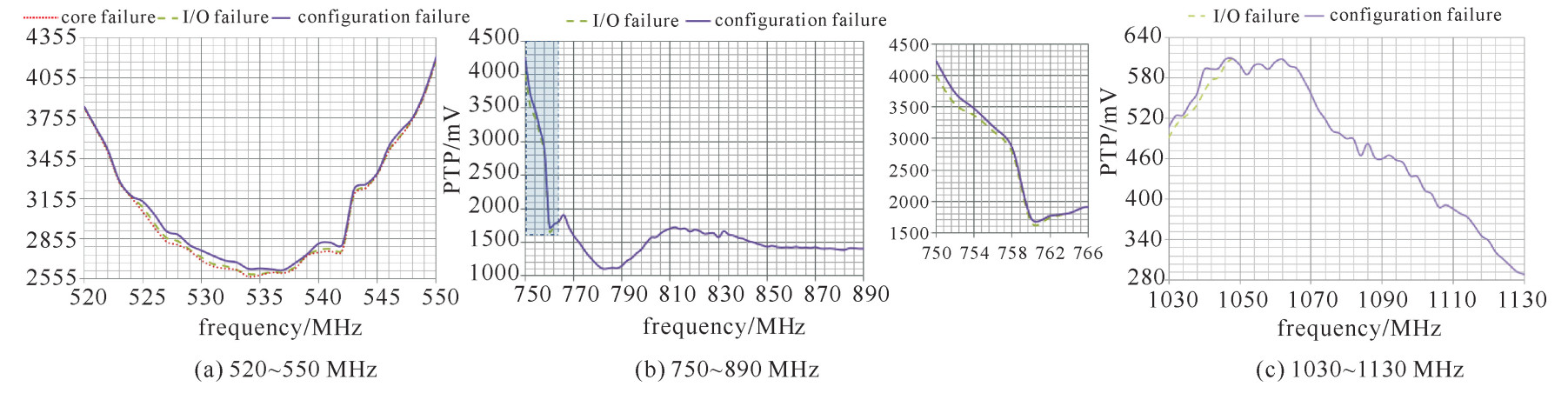

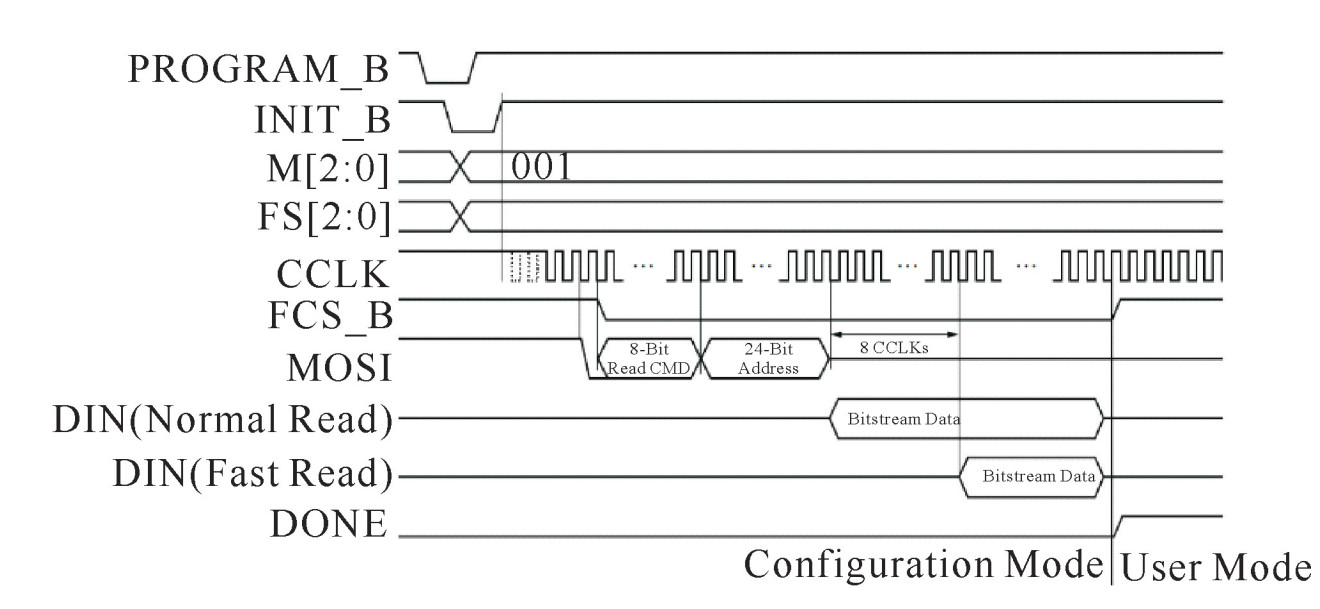

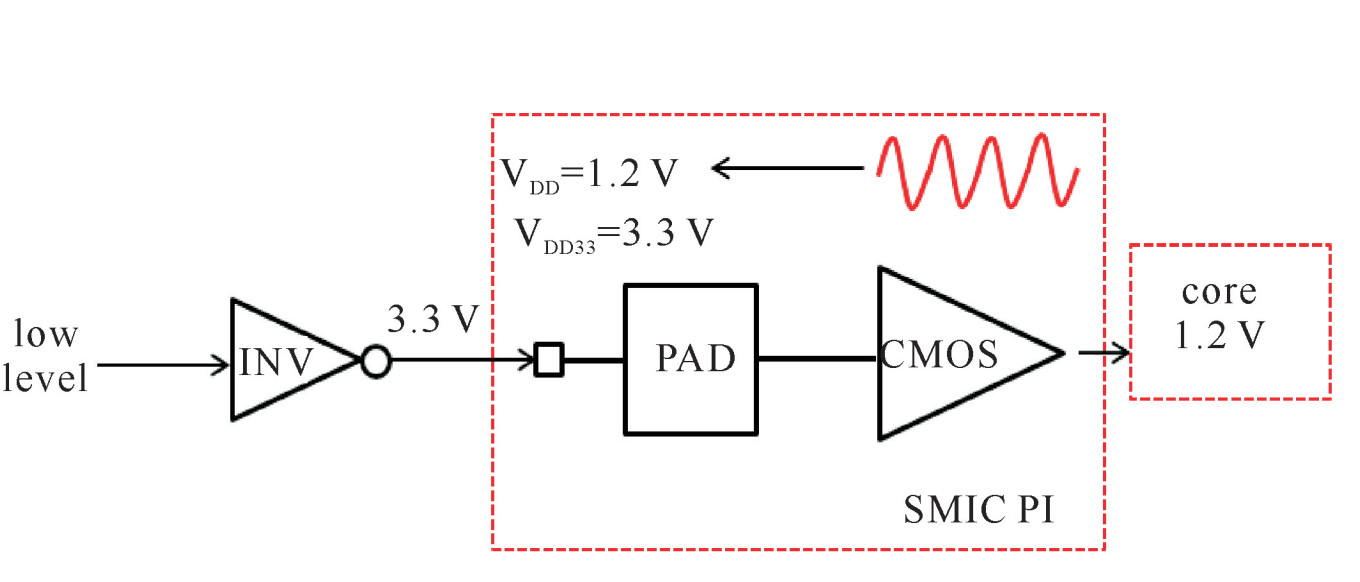

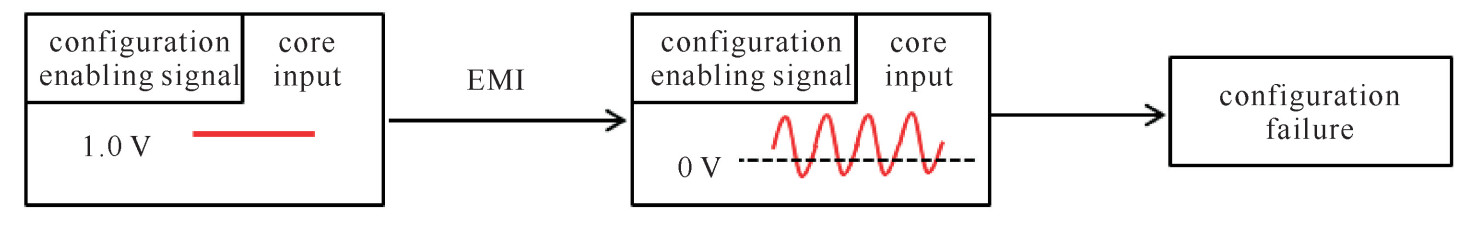

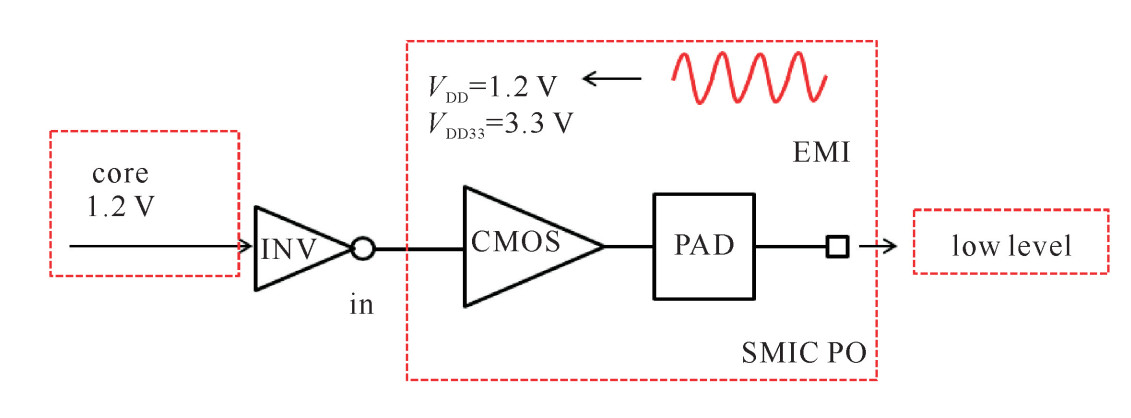

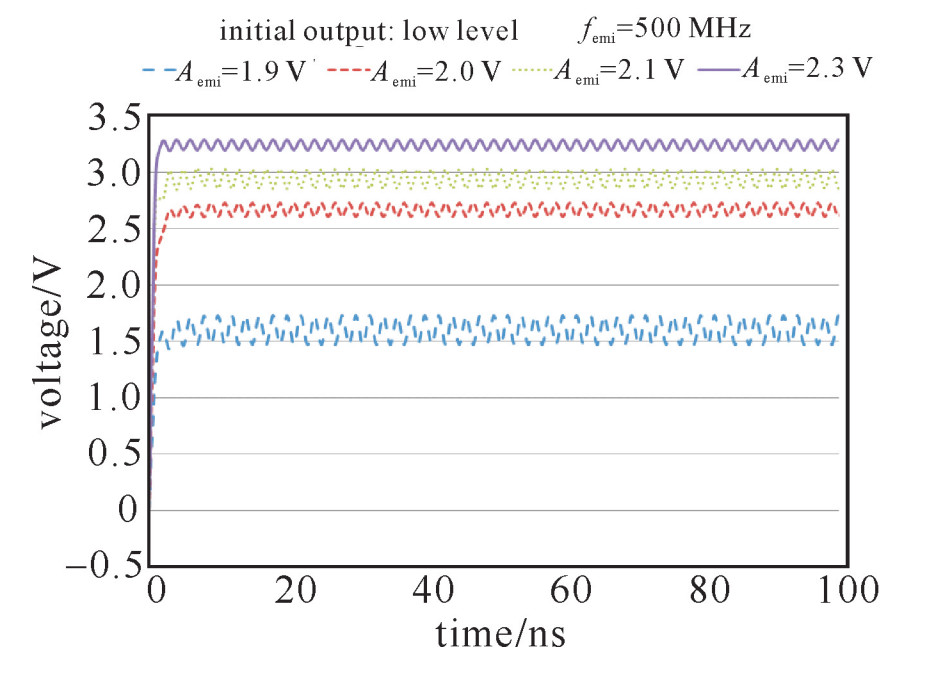

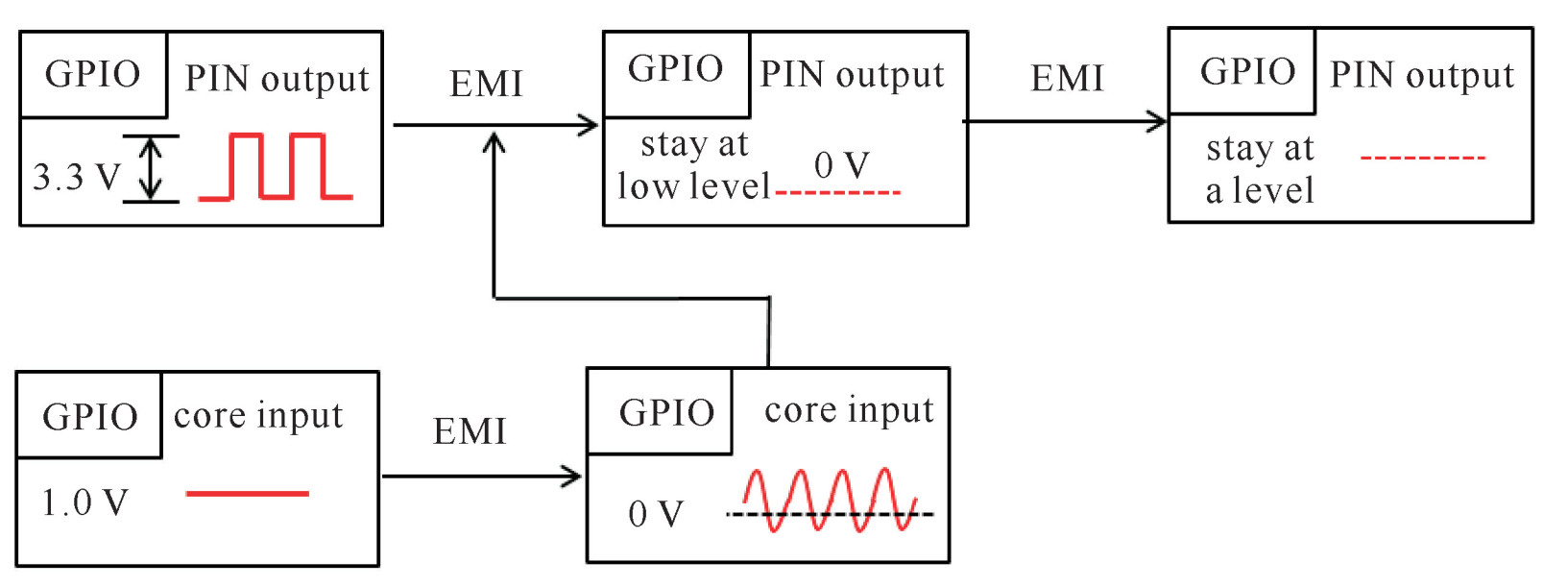

摘要: 研究了一种Xilinx公司FPGA芯片XC7A200T-2FBG676在射频干扰下的失效机理。通过对该FPGA内核供电引脚注入射频干扰发现,某些频率下,随着干扰强度的增大,FPGA会依次出现三种不同类型的失效,分别为该FPGA的内核失效、I/O失效和配置失效。测试分析和HSPICE仿真表明,内核失效是由于BRAM的逻辑层抗扰性差所致,I/O失效是由于射频干扰下输入/输出信号的同时失真所致,配置失效则是由于配置系统读取错误的配置使能信号所致。研究可为该FPGA芯片或者系统电磁兼容设计以及该FPGA抗扰性检测方案的制定提供指导。Abstract: The failure mechanism of Xilinx's FPGA chip XC7A200T-2FBG676 under RF interference is studied. When RF interference injects into the power supply pins of the FPGA core, it is found that with the increase of interference intensity at the some frequencies, three types of FPGA failures occur successively, namely core failure, I/O failure and configuration failure. Test analysis and HSPICE simulation show that the core failure is due to the poor disturbance immunity of the logic layer of BRAM, the I/O failure is due to the simultaneous distortion of input/output signals under RF interference, and the configuration failure is due to the configuration system reading the wrong configuration enable signal. This study could provide guidance for the electromagnetic compatibility design of this kind of FPGA chip or system, as well as the formulation of electromagnetic immunity detection scheme of this kind of FPGA.

-

Key words:

- FPGA /

- radio-frequency interference /

- FPGA core /

- FPGA failure

-

闭合磁芯脉冲变压器因其具有结构简单、重复频率运行能力强、能量传输效率高等特点,被广泛用作重复频率脉冲功率系统的升压器件[1-3]。常用于脉冲变压器的磁芯材料有铁氧体、坡莫合金、铁基非晶、铁基纳米晶以及硅钢等。为了减小磁芯的体积,要求脉冲变压器工作时磁感应强度增量ΔB尽可能大,这就需要通过复位电路将磁芯复位到反向饱和点,使磁芯工作时由反向饱和点向正向饱和点励磁。磁芯复位的方式大体上分为自复位和外加复位两种,自复位电路利用储能电容的充电电流进行去磁,适用于小功率的脉冲变压器,对于大功率脉冲变压器,需采用外加的复位电路。传统的外加复位电路是给磁芯外加一复位绕组,与变压器主绕组隔离,复位绕组通一恒定大小的直流电流[4-5]。这种电路虽然结构简单,但复位绕组匝数较少时需要较大的复位电流,增加复位绕组匝数又会感应较高的电压,不宜用于脉冲变压器的磁芯复位。本文研究了一种重复频率脉冲复位电路,并应用到极薄硅钢带环形磁芯脉冲变压器中,有效提高了复位电路的能量利用率,提高了脉冲变压器输出电压的稳定性。

1. 磁芯复位原理

脉冲变压器工作时,其磁芯的伏秒积应该满足[3]

(1) 式中:ΔBm为磁芯的最大磁感应强度增量;N2为变压器副边匝数;S为磁芯截面积;kT为磁芯的叠装系数;U2为副边电压;tm为副边电压达到最大值的时间。

对于脉冲变压器来说,希望磁芯材料的饱和磁感应强度Bs较高而剩余磁感应强度Br低,且矫顽力Hc尽量小。与其他材料相比,极薄硅钢的Bs和Br参数值都较高,如果工作前不进行磁芯复位,其磁感应强度增量ΔBm=Bs-Br(0.2~0.4 T),磁芯利用率很低;反之,如果工作前对磁芯进行复位,则其最大磁感应强度增量ΔBm=Bs+Br(3.0~3.4 T),使磁芯得到充分的利用[6]。

传统的外加磁芯复位电路是给复位绕组通一持续且恒定的电流,如图 1(a)所示。图中加入了扼流电感、限流电阻、吸收电容以及电荷泄放回路,用来保护直流电源。复位电流Ir=Hmlm/Nr,其中,Hm一般取为磁芯矫顽力的1~1.5倍[7],lm为磁芯的平均磁路长度,Nr为复位绕组匝数。具有较大输出电流的恒流源结构复杂且价格昂贵。为了降低复位电流,常需要增大复位绕组匝数,这使得脉冲变压器主放电回路工作时在复位绕组两端感应出很高的电压,对直流源的高压保护提出了更高的要求。长时间运行时,这种复位电路有很大一部分能量转换成焦耳热,效率较低。

脉冲复位电路[8-9]是给复位绕组通一脉冲电流,使磁芯复位到反向饱和点并最终停留在反向剩磁点,其原理如图 1(b)所示。由于该电路只是在需要复位的时候工作,降低了非工作时间段电能的损耗,提高了效率。复位电路工作时,先触发开关K1导通,给复位储能电容Cr充电;然后,使开关K1断开而K2导通,Cr对复位绕组放电,放电电流与脉冲变压器主放电电流相反,实现复位。反并联二极管D1用于保护复位电容,防止其承受反压。该回路中,开关管K1采用IGBT,可比较精确地控制Cr的充电时间,并在K2导通前可靠关断;K2采用SCR,脉冲复位电流过零时自动关断,避免复位电流反向。开关管触发信号及时序如图 2所示。所选型号为FGA25N120ANTD,其开启电压UGE(th)为5 V,利用其结电容泄放电荷的时间控制IGBT的导通时间,所以该触发信号波形为指数波。SCR为电流触发型器件,触发信号由电容器对一匝数比为10∶2的小磁环脉冲变压器的原边放电产生,经变流放大后由G极流入,这里测量的是变压器副边的开路电压,近似为脉宽几十μs的矩形脉冲。

2. 磁芯脉冲复位试验结果及分析

本应用选择的磁芯由厚度为50 μm的GT-050型硅钢薄带叠绕制成,其最适工作频率可达到40 kHz,铁损小于1 W/kg,可加工性能较好[10]。根据脉冲变压器带载能力的要求设计的磁芯结构尺寸为:外直径28 cm,内直径14 cm,高度为7 cm,叠装系数大于0.9。

2.1 单次复位试验

为了使脉冲变压器工作时在复位绕组两端感应的电压较低,复位绕组选为1匝;为了降低复位电路工作时变压器副边感应的电压,复位电容选用mF级的电解电容,充电电压不高于150 V;为了使相邻两次复位工作的最大磁感应强度增量相同(近),每次复位后更换复位绕组电流的流入端。按图 1 (b)所示的原理图搭建复位电路,脉冲变压器原、副边绕组均开路,用TPP1000电压探头测量复位绕组两端的电压、Pearson 4191电流传感器测量流过复位绕组的电流、DPO4104B数字示波器读取波形数据。通过试验研究了复位电容和充电电压的大小对复位效果的影响,试验结果如图 3所示。

图 3(a)所示为当复位电容为1.5 mF、充电电压为150 V时复位绕组两端电压和流过复位绕组的电流的波形。图中用不同颜色的箭头标示了磁芯复位过程的三个阶段,分别对应B-H曲线的三段:第一段,磁芯未饱和阶段(绿色箭头),磁化电感很大,电流很小;第二段,磁芯趋于饱和阶段(蓝色箭头),饱和电感很小,电流快速增大,电压快速降低;第三段,恢复到反向剩磁阶段,电流开始减小,电压反向。可以看出,当脉冲变压器磁芯饱和时,瞬时脉冲电流变得很大,但其持续时间不到1 ms,对于50 Hz重复频率来说,平均电流很小,电能损耗很低。图 3(b)所示为改变复位电容和充电电压后测得的复位绕组两端的电压,可以看出,充电电压越低、复位电容量越大时,复位绕组两端电压波形的脉宽越宽,复位所需的时间越长。对比同一电容量不同电压下的情况,分析可知,磁芯复位到反向剩磁点需要足够的能量,1.5 mF/24 V时已无法使磁芯完全复位。利用图 3(b)中的波形,将电压波形的第一个半波伏秒积计算出来得到如表 1的结果。从表中计算数据可以看出,1.5 mF/100 V条件下的伏秒积和11 mF/24 V条件下的相近,不同的是后者复位时间大约3 ms,而前者只有0.5 ms。而为了避免复位时变压器副边感应出较高的电压,希望复位电压尽可能低,且3 ms的复位时间对于50 Hz重复频率来说是充裕的,因此选用后者作为复位电路的基本参数。

表 1 不同电容电压下磁芯的伏秒积Table 1. Voltage-second product of magnetic coreCr / UCr voltage-second product /(kV·μs) 1.5 mF/150 V 30.48 1.5 mF/100 V 30.09 1.5 mF/24 V 5.28 6.6 mF/24 V 29.52 11 mF/24 V 30.12 为了进一步探究到底是电荷量还是复位电容储存的能量影响复位效果,进行了电路仿真分析,分别保证Cr储存的电荷量和电能一定,监测变压器最大磁感应强度,结果如表 2所示。比较后可以看出,相同能量的复位回路具有比较接近的复位效果,且随着电压的降低(电容量的增大),效果逐渐变差;电荷量相同时,电压越低且电容量越高,则复位效果越差。

表 2 复位效果影响因素Table 2. Simulated effectiveness of reset circuitQ=CrUCr maximum magnetic induction Bm / T W=(CrUCr2)/2 maximum magnetic induction Bm / T 0.3 mF×200 V 1.78 0.3 mF×200 V 1.78 1.5 mF×40 V 1.70 1.5 mF×90 V 1.77 3 mF×20 V 1.43 3 mF×65 V 1.76 8 mF×7.5 V 0.81 8 mF×40 V 1.74 - - 16 mF×28 V 1.71 从上述分析可知,在选择复位回路参数时,应综合考虑复位时间和复位过程对输出电压的影响,选择合适的复位储能电容容量和充电电压。一般的,当重复频率较高时,复位电容容量要小,充电电压要高一些。如果只是单次运行,又要求复位过程不影响脉冲变压器输出,则可选择较大容量的复位电容而降低其充电电压。

2.2 单次复位下脉冲变压器磁化特性测试

在上述电路的基础上,加入变压器主放电回路后进行了有复位和无复位时脉冲变压器磁化特性测量[11]的对比试验,原边和副边各绕2匝,原边电容60 μF,充电1000 V,用P6105A高压探头测量副边开路电压,测试电路如图 4所示。无复位时,原边电容充电完成后直接手动触发球隙开关;有复位时,先触发复位回路开关导通,复位完成后再触发球隙开关。测量的电压波形如图 5所示。对比分析可知,加入复位电路后,变压器输出电压的正半波伏秒积增大了近10倍,带负载能力得到很大的提高。多次试验结果表明,有复位时,副边开路电压更稳定。因此,在同等负载条件下,采用复位电路后,可以减小磁芯的体积,使装置更加紧凑和小型化,输出更加稳定。

2.3 重复频率运行下复位试验

复位电路在50 Hz重复频率下运行时,测得复位电容两端的电压波形如图 6所示。图 6(a)为第一个脉冲的展开图,可以看出,复位电容大概在6 ms(T1)内充到25 V,经过一段稳定期T2后,在2 ms (T3)内放电结束,完成第一次复位。在T2期间内,复位电容两端的电压稍有降低,因此应尽可能缩短这一时间(控制K1和K2的导通时序)。整体来看,重复频率运行时,后序的复位电容两端的电压稍有降低,并最终稳定在约23 V,可以满足对磁芯完全复位的需要。对该复位电路进行了长时间重复频率运行试验,试验结果表明,该复位电路在50 Hz重复频率下能够长时间稳定运行,选择的复位电容器比较合理。

3. 结论

所选脉冲变压器磁芯的饱和磁感应强度和剩余磁感应强度都较大,需要引入复位电路来提高磁芯利用率。采用脉冲复位的方式,对极薄硅钢带环形磁芯的重复频率复位电路进行了研究和分析。通过增大复位电容的容量,降低了复位电容的充电电压,使得复位电路工作时脉冲变压器副边感应的电压降低,有利于变压器主放电脉冲对负载电容的充电。所设计的复位电路能够在50 Hz重复频率下长时间稳定运行。需要进一步优化复位电路开关管的导通时序,降低复位电容两端电压维持阶段的电压跌落。

-

-

[1] Christopoulos C. Electromagnetic compatibility (EMC) in challenging environments[M]. Springer International Publishing, 2017. [2] 黎明, 黄如. 后摩尔时代大规模集成电路器件与集成技术[J]. 中国科学: 信息科学, 2018, 48(8): 963-977. https://www.cnki.com.cn/Article/CJFDTOTAL-PZKX201808001.htmLi Ming, Huang Ru. Device and integration technologies for VLSI in post-Moore era. Scientia Sinica: Informationis, 2018, 48(8): 963-977 https://www.cnki.com.cn/Article/CJFDTOTAL-PZKX201808001.htm [3] Coulson D R. EMC-hardening microprocessor-based systems[C]//IEE Colloquium on Achieving Electromagnetic Compatibility: Accident or Design. 1997. [4] Fiori F, Musolino F. Analysis of EME produced by a microcontroller operation[C]//Proceedings Design, Automation and Test in Europe Conference and Exhibition. 2001. [5] Su T, Unger M, Steinecke T, et al. Using Error-Source Switching (ESS) concept to analyze the conducted radio frequency electromagnetic immunity of microcontrollers[J]. IEEE Transactions on Electromagnetic Compatibility, 2012, 54(3): 634-645. doi: 10.1109/TEMC.2011.2165341 [6] Dehbaoui A, Dutertre J M, Robisson B, et al. Electromagnetic transient faults injection on a hardware and a software implementations of AES[C]//Fault Diagnosis and Tolerance in Cryptography (FDTC). 2012. [7] Zussa L, Dehbaoui A, Tobich K, et al. Efficiency of a glitch detector against electromagnetic fault injection[C]//Conference on European Design and Automation Association. 2014. [8] Ren L, Li T, Chandra S. Prediction of power supply noise from switching activity in an FPGA[J]. IEEE Transactions on Electromagnetic Compatibility, 2014, 56(3): 699-706. doi: 10.1109/TEMC.2013.2293872 [9] 程俊平, 周长林, 余道杰, 等. 基于供电网络传导耦合的FPGA电磁敏感特性分析[J]. 强激光与粒子束, 2019, 31: 023202. doi: 10.11884/HPLPB201931.180322Cheng Junping, Zhou Changlin, Yu Daojie, et al. Electromagnetic susceptibility analysis of FPGA based on conducted coupling of power supply network. High Power Laser and Particle Beams, 2019, 31: 023202 doi: 10.11884/HPLPB201931.180322 [10] Xilinx Inc. Series FPGAs Configuration User Guide. Version[EB/OL]. http://china.xilinx.com/support/documentation/user_guides/ug470_7Series_Config.pdf. -

下载:

下载:

下载:

下载: