| [1] |

梁琳, 余岳辉. 半导体脉冲功率开关发展综述[J]. 电子电力技术, 2012, 46(12):42-45. (Liang Lin, Yu Yuehui. Review on development of semiconductor pulse power switches[J]. Power Electronics, 2012, 46(12): 42-45

|

| [2] |

Grekhov I V, KardoSysoev A F. Sub-nanosecond current drops in delayed breakdown of silicon p-n junction[J]. Sov Tech Phys Lett, 1979, 5(8): 395-396.

|

| [3] |

Grekhov I V, KardoSysoev A F, Kostina L S, et al. High-power subnanosecond switches[J]. Electronics Letters, 1981, 17(12): 422-423. doi: 10.1049/el:19810293

|

| [4] |

Focia R J, Schamiloglu E, Fleddermann C B. Simple techniques for the generation of high peak power pulses with nanosecond and subnanosecond rise times[J]. Rev Sci Instrum, 1996, 67(7): 2626-2629. doi: 10.1063/1.1147191

|

| [5] |

Grekhov I V. Pulse power generation in nano-and subnanosecond range by means of ionizing fronts in semiconductors: the state of the art and future prospects[J]. IEEE Trans Plasma Science, 2010, 38(5): 1118-1123. doi: 10.1109/TPS.2010.2043857

|

| [6] |

Grekhov I V, Mesyats G A. Physical basis for high-power semiconductor nanosecond opening switches[J]. IEEE Trans Plasma Science, 2000, 28(5): 1540-1544. doi: 10.1109/27.901229

|

| [7] |

Lyublinsky A G, Korotkov S V, Aristov Y V, et al. Pulse power nanosecond-range DSRD-based generators for electric discharge technologies[J]. IEEE Trans Plasma Science, 2013, 41(10): 2625-2629. doi: 10.1109/TPS.2013.2264328

|

| [8] |

Nikoo M S, Hashemi S M, Dilmaghanian M O. DSRD-based high-power repetitive short-pulse generator containing GDT: Theory and experiment[J]. IEEE Trans Plasma Science, 2017, 45(8): 2341-2350. doi: 10.1109/TPS.2017.2717047

|

| [9] |

Ivanov P, Kon'kovb O, Samsonovac T. Electrical performance of 4H-SiC based drift step recovery diodes[J]. Materials Science Forum, 2016, 858: 761-764. doi: 10.4028/www.scientific.net/MSF.858.761

|

| [10] |

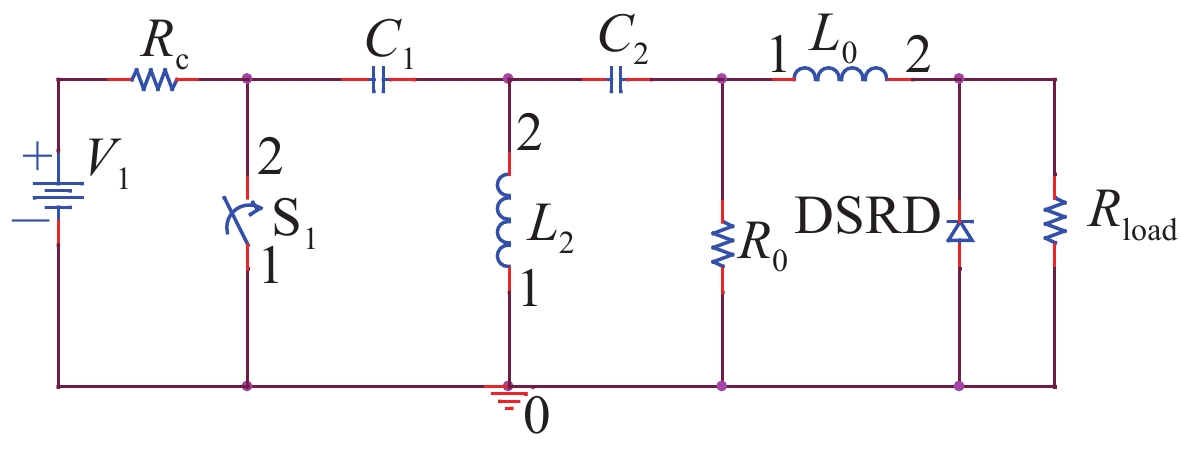

王亚杰, 何鹏军, 荆晓鹏, 等. 基于漂移阶跃恢复二极管开关的脉冲源仿真计算[J]. 强激光与粒子束, 2018, 30:095005. (Wang Yajie, He Pengjun, Jing Xiaopeng, et al. Simulation and calculation of pulsed power source based on drift step recovery diode switching[J]. High Power Laser and Particle Beams, 2018, 30: 095005

|

| [11] |

方旭, 丁臻捷, 浩庆松, 等. 基于DSRD的高重频亚纳秒脉冲产生方法研究[C]//第四届全国脉冲功率会议. 2015.Fang Xu, Ding Zhenjie, Hao Qingsong, et al. Study on generation of drift step diodes for sub-nanosecond switching and high repetition rate operation//The 4th China Pulse Power Conference. 2015

|

| [12] |

马红梅, 刘忠山, 杨勇, 等. 新型亚纳秒半导体切断开关研制[J]. 器件制造与应用, 2010, 35(4):337-339. (Ma Hongmei, Liu Zhongshan, Yang Yong, et al. Design and manufacture of novel sub-nanosecond opening semiconductor switch[J]. Manufacturing and Application of Device, 2010, 35(4): 337-339

|

| [13] |

梁勤金, 石小燕, 曹晓阳. 一种快速离化波开关及其在高压脉冲源中的应用[J]. 电讯技术, 2010, 50(5):68-71. (Liang Qinjin, Shi Xiaoyan, Cao Xiaoyang. A fast ionization wave switch and its application in high voltage pulser[J]. Telecommunication Engineering, 2010, 50(5): 68-71 doi: 10.3969/j.issn.1001-893x.2010.05.015

|

下载:

下载: