Design of drift step recovery diode pulse power generator based on magnetic saturation transformer

-

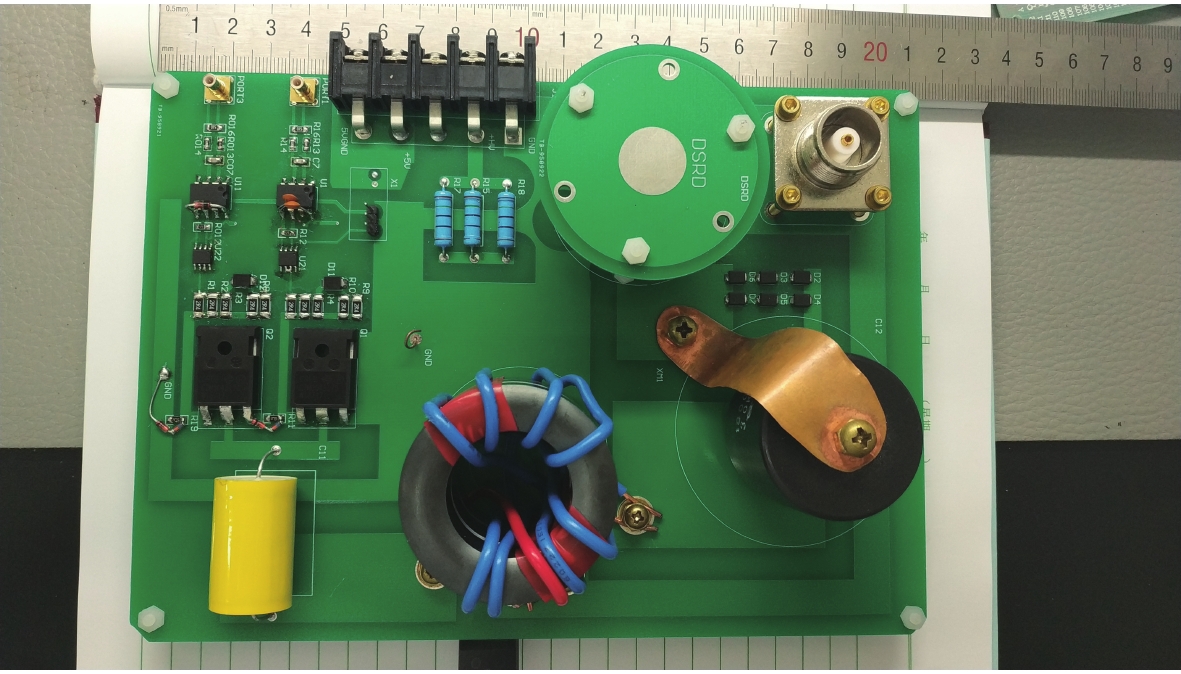

摘要: 漂移阶跃恢复二极管(DSRD)具有开关速度快、重频高、工作电流大等优点,在脉冲功率技术中很有应用前景。研究了一种基于磁饱和变压器的DSRD泵浦电路拓扑结构,具有体积小、重量轻、可靠性高等特点。根据DSRD的工作要求,采用功率MOSFET作为初级开关,结合磁饱和变压器的升压和磁开关特性,设计了DSRD的泵浦电路。利用Pspice软件对电路进行了仿真分析,验证了电路原理的正确性。在仿真分析的基础上,完成了一台原理样机的设计和电路实验。实验结果表明,该电源样机在前级充电电压800 V条件下,50 Ω负载上产生的脉冲幅值大于7 kV,前沿小于4.2 ns(10%~90%),半高宽约10 ns。Abstract: Drift step recovery diode (DSRD) has a great application prospect in pulse power technology for its notably short switching-off time, high repetition rate and large working current. In this paper, a DSRD pump circuit topology based on magnetic saturation transformer is studied. The topology is small, light and reliable. According to the operating requirements of DSRD, a pump circuit was designed. It consists of a power MOSFET primary switch and a magnetic saturation transformer with boost and saturation characteristics. The circuit was simulated by Pspice software, which confirmed the principles of the circuit. Based on the simulation analysis, a prototype was designed and its circuit experiment was implemented. The experiment indicates that when the charging voltage is 800 V, the pulse amplitude on resistor load of 50 Ω is larger than 7 kV, the rise time is less than 4.2 ns (10%−90%) and the FWHM is about 10 ns.

-

表 1 DSRD主要特征参数

Table 1. The main parameters of DSRD

no. paramaters symbol test conditions bridge limit unit minimum maximum 1 positive voltage VF IF=10 mA − 8 V 2 reverse current IR VR=500 V − 1 mA 3 breakdown voltage V(BR) IR=5 mA 1 000 − V 4 pulse voltage Vp i≥300 A 10 − kV 5 pulse current i Vp≥10 kV 300 − A 6 rise time tr Vp=10 kV − 3 ns 7 repetitive frequency fR Vp=10 kV,tr≤3 ns 10 − kHz -

[1] 陈锦晖, 王磊, 施华, 等. HEPS在轴注入冲击器系统及快脉冲电源样机研制[J]. 强激光与粒子束, 2019, 31:040017. (Chen Jinhui, Wang Lei, Shi Hua, et al. Application of fast pulsed power supply to high energy photon source[J]. High Power Laser and Particle Beams, 2019, 31: 040017 doi: 10.11884/HPLPB201931.190007 [2] 刘锡三. 高功率脉冲技术[M]. 北京: 国防工业出版社, 2005.Liu Xisan. High pulsed power technology[M]. Beijing: National Defense Industry Press, 2005 [3] Cook E G. Review of solid-state modulators[C]//Proc of XX International Linac Conference. 2000 [4] 吴佳霖, 刘英坤. 高功率半导体开关器件DSRD的研究进展[J]. 微纳电子技术, 2015, 52(4):311-215, 250. (Wu Jialin, Liu Yingkun. Research development of the high power semiconductor switching device DSRD[J]. Micronanoelectronic Technology, 2015, 52(4): 311-215, 250 [5] 梁勤金, 邓晓磊, 石小燕, 等. 新型半导体开关高压电磁脉冲产生技术[J]. 强激光与粒子束, 2012, 24(2):497-500. (Liang Qinjin, Deng Xiaolei, Shi Xiaoyan, et al. High voltage electromagnetic pulse generation using semiconductor switches[J]. High Power Laser and Particle Beams, 2012, 24(2): 497-500 doi: 10.3788/HPLPB20122402.0497 [6] Krasnykh A. Overview of driver technologies for nanosecond TEM kickers[C]//Proceedings of the 7th International Particle Accelerator Conference. 2016, 3645-3647. [7] Benwell A, Burkhart C, Krasnykh A, et al. A 5kV, 3MHz solid-state modulator based on the DSRD switch for an ultra-fast beam kicker[C]//IEEE Power Modulator and High Voltage Conference. 2013: 328-331. [8] Lyublinsky A G, Korotkov S V, Aristov Y V, et al. Pulse power nanosecond-range DSRD-based generators for electric discharge technologies[J]. IEEE Trans Plasma Science, 2013, 41(10): 2625-2629. doi: 10.1109/TPS.2013.2264328 [9] Grekhov I V, Mesyats G A. Physical basis for high-power semiconductor nanosecond opening switches[J]. IEEE Trans Plasma Science, 2000, 28(5): 1540-1544. doi: 10.1109/27.901229 [10] Brylevsky V I, Efanov V M, Kardo-Sysyev A F, et al. Power nanosecond semiconductor opening plasma switches[J]//Proceedings of IEEE International Power Modulator Symposium. 1996: 51-54. [11] 张玲, 周斌, 谢义方, 等. 基于漂移阶跃恢复二极管的超宽带探地雷达发射技术[J]. 强激光与粒子束, 2009, 21(12):1854-1858. (Zhang Ling, Zhou Bin, Xie Yifang, et al. Transmitter techniques for ultra-wideband ground penetrating radar based on drift step recovery diodes[J]. High Power Laser and Particle Beams, 2009, 21(12): 1854-1858 [12] Min B D, Kim J H, Pavlov E, et al. A compact inductive type pulse generator using diodes as opening switch[C]//IEEE Pulsed Power Conference. 2005: 1364-1367. [13] Korotkov S V, Aristov Y V, Voronkov V B, et al. A small dynistor generator of high-power nanosecond pulses[J]. Instruments and Experimental Techniques, 2018, 61(1): 44-46. doi: 10.1134/S0020441217060057 [14] Korotkov S V, Aristov Y V, Voronkov V B, et al. Semiconductor switches of laser pumping pulses of nanosecond duration[J]. Instruments & Experimental Techniques, 2009, 52(5): 699. -

下载:

下载: